## **DOT/FAA/AR-05/52**

Office of Aviation Research and Development Washington, D.C. 20591

# Safety and Certification Approaches for Ethernet-Based Aviation Databuses

December 2005

Final Report

This document is available to the U.S. public through the National Technical Information Service (NTIS), Springfield, Virginia 22161.

U.S. Department of Transportation Federal Aviation Administration

#### NOTICE

This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The United States Government assumes no liability for the contents or use thereof. The United States Government does not endorse products or manufacturers. Trade or manufacturer's names appear herein solely because they are considered essential to the objective of this report. This document does not constitute FAA certification policy. Consult your local FAA aircraft certification office as to its use.

This report is available at the Federal Aviation Administration William J. Hughes Technical Center's Full-Text Technical Reports page: actlibrary.tc.faa.gov in Adobe Acrobat portable document format (PDF).

**Technical Report Documentation Page** 1. Report No. 2. Government Accession No. DOT/FAA/AR-05/52 4. Title and Subtitle 5. Report Date December 2005 SAFETY AND CERTIFICATION APPROACHES FOR ETHERNET-BASED 6. Performing Organization Code **AVIATION DATABUSES** 8. Performing Organization Report No. 7. Author(s) Yann-Hang Lee<sup>1</sup>, Elliott Rachlin<sup>2</sup>, and Philip A. Scandura, Jr.<sup>2</sup> 9. Performing Organization Name and Address 10. Work Unit No. (TRAIS) <sup>2</sup>Honeywell Laboratories <sup>1</sup>Arizona State University 2111 N. 19<sup>th</sup> Avenue 11. Contract or Grant No Office of Research and Sponsored Projects Phoenix, AZ 85027 Box 873503 Tempe, AZ 85287-3503 13. Type of Report and Period Covered 12. Sponsoring Agency Name and Address U.S. Department of Transportation Final Report Sponsoring Agency Code Federal Aviation Administration Office of Aviation Research and Development AIR-120 Washington, DC 20591 15. Supplementary Notes The Federal Aviation Administration Airport and Aircraft Safety R&D Division COTR was Charles Kilgore. With the advent of higher-performance computing and communication systems, aircraft will have the capability to process an unprecedented amount of information pertaining to performance, safety, and efficiency. Flight instruments will be integrated to share information and to cooperate with each other. It is inevitable that a high-speed and versatile network infrastructure will be required in the next generation of aircraft. One commercial off-the-shelf technology, Ethernet, is seen as potentially attractive in avionics systems due to its high bandwidth, low wire count, and low cost. Ethernet has been used in the Boeing 777 to transmit non-flight-critical data and in the Boeing 767ER within a flight-critical display system. There are many safety concerns, however, when Ethernet is applied to flight-critical systems. The inherent nature of the Ethernet protocols can easily result in nondeterministic behavior and interference. These are significant technical hurdles that must be overcome before Ethernet will be a viable candidate as an aviation databus technology. In this report, safety and certification issues of Ethernet-based aviation databuses are summarized. Initially, it focuses on the issues of deterministic operations of Ethernet controller, device drivers, and communication stack, and possible solutions to avoid any adverse effects. In the latter part of the report, the discussion is centered on the evaluation criteria for the certifiability of Ethernetbased databuses. A prototype communication subsystem, to support deterministic data delivery in Ethernet, is also illustrated. Using this proposed design as an example, the report explains how the specific avionics requirements can be satisfied. Finally, it describes the implementation of the design on a test bed and analysis of the final results. 17. Key Words 18. Distribution Statement Ethernet, Determinism, Software, Databus, Network, Criteria, This document is available to the public through the

National Technical Information Service (NTIS) Springfield,

22. Price

21. No. of Pages

124

Virginia 22161

20. Security Classif. (of this page)

Unclassified

Communication, Avionics

19. Security Classif. (of this report)

Unclassified

# TABLE OF CONTENTS

|     |                                                                                                                                        |                                           |                                                                                                                                                                                           | Page                                   |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| EXE | CUTIVI                                                                                                                                 | E SUMN                                    | MARY                                                                                                                                                                                      | xiii                                   |  |

| 1.  | INTR                                                                                                                                   | INTRODUCTION                              |                                                                                                                                                                                           |                                        |  |

|     | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                                                                                                 | Why I<br>Why I<br>An Ov<br>Repor<br>Focus | Ethernet is Being Proposed for Use on Aircraft This Research is Needed Verview of This Research Project t Organization for Readers  Readers Concerned With Ethernet Databus Qualification | 1-1<br>1-2<br>1-2<br>1-2<br>1-5<br>1-6 |  |

|     |                                                                                                                                        | 1.6.2                                     | Readers Concerned With Ethernet Databus Development                                                                                                                                       | 1-6                                    |  |

| 2.  | ETH                                                                                                                                    | ERNET-                                    | BASED DATABUS SYSTEM MODEL                                                                                                                                                                | 2-1                                    |  |

| 3.  | TRAFFIC ANALYSIS                                                                                                                       |                                           |                                                                                                                                                                                           | 3-1                                    |  |

|     | <ul> <li>3.1 Overview of the Traffic Analysis</li> <li>3.2 Computation Environment</li> <li>3.3 Summary of Analysis Results</li> </ul> |                                           | 3-1<br>3-2<br>3-2                                                                                                                                                                         |                                        |  |

| 4.  | DETERMINISM IN COMMUNICATION SYSTEM                                                                                                    |                                           |                                                                                                                                                                                           | 4-1                                    |  |

|     | 4.1<br>4.2                                                                                                                             |                                           | eterminism<br>nalysis of Nondeterminism in the Host—Hardware Components                                                                                                                   |                                        |  |

|     |                                                                                                                                        | 4.2.1                                     | Interrupt Chaining Latency                                                                                                                                                                | 4-2                                    |  |

|     |                                                                                                                                        | 4.2.2                                     | Interrupt Latency From Lock and Demand Legacy DMA Modes                                                                                                                                   | 4-3                                    |  |

|     |                                                                                                                                        | 4.2.3                                     | Interrupt Latency From Context Switching                                                                                                                                                  | 4-3                                    |  |

|     |                                                                                                                                        | 4.2.4                                     | Virtual Memory and Noncontiguous Buffers                                                                                                                                                  | 4-3                                    |  |

|     |                                                                                                                                        | 4.2.5                                     | Latency From Non-Pre-Emptive DMA Mechanism                                                                                                                                                | 4-4                                    |  |

|     |                                                                                                                                        | 4.2.6                                     | Disparity Between the Half-Duplex PCI Bus and Full-Duplex Ethernet Controller                                                                                                             | 4-4                                    |  |

|     |                                                                                                                                        | 4.2.7                                     | The PCI Bus Arbitration Latency                                                                                                                                                           | 4-4                                    |  |

|     |                                                                                                                                        | 4.2.8                                     | Latency of PCI Burst Read/Write Process                                                                                                                                                   | 4-4                                    |  |

|    | 4.3        | Analy            | sis of Nondeterminism in the Host—Software Components                                     | 4-5        |

|----|------------|------------------|-------------------------------------------------------------------------------------------|------------|

|    |            | 4.3.1<br>4.3.2   | The CSMA/CD Protocol Internet Protocol/Address Resolution Protocol                        | 4-5<br>4-6 |

|    |            | 4.3.3            |                                                                                           | 4-6        |

|    | 4.4        | Possib           | ble Control/Mitigation Techniques                                                         | 4-7        |

|    |            | 4.4.1            | Ethernet MAC Controller Traffic Smoother                                                  | 4-7<br>4-9 |

|    |            |                  | Recommendations on Network Stacks and Ethernet Drivers                                    | 4-10       |

| 5. | ANA        | LYSIS (          | OF DETERMINISTIC DATA COMMUNICATION                                                       | 5-1        |

|    | 5.1        | Deterr           | Deterministic Message Transmission in Ethernet Bus                                        |            |

|    |            | 5.1.1<br>5.1.2   | Delay Arbitration Protocol<br>Real-Time Ethernet                                          | 5-1<br>5-1 |

|    |            |                  |                                                                                           |            |

|    | 5.2        | Deterr           | ministic Message Transmission in Switched Network                                         | 5-2        |

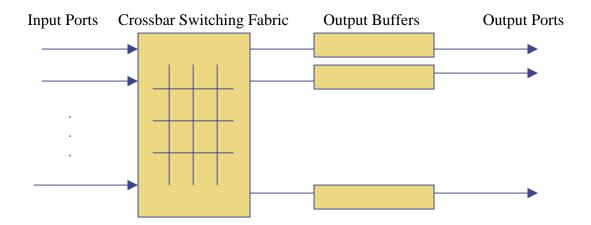

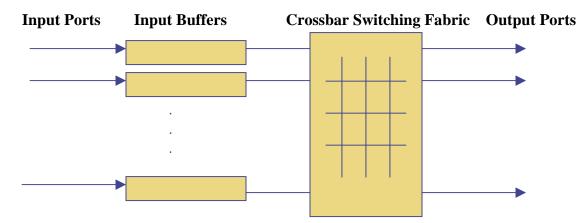

|    |            | 5.2.1            | Switch Architectures                                                                      | 5-2        |

|    |            | 5.2.2            | Analysis Tool—Network Calculus                                                            | 5-2        |

|    |            | 5.2.3            | Performance-Guaranteed Service Disciplines                                                | 5-3        |

|    |            | 5.2.4            | Multicast Switches                                                                        | 5-6        |

|    |            | 5.2.5            | Integrating Unicast and Multicast Traffic Scheduling With Parallel Switching Architecture | 5-8        |

| 5. | DATA       | ABUS E           | EVALUATION AND QUALIFICATION                                                              | 6-1        |

|    | 6.1<br>6.2 | Backg<br>Certifi | ground<br>ication Authorities Position Paper                                              | 6-1<br>6-1 |

|    | 6.3        | Certifi          | ication Considerations                                                                    | 6-2        |

|    | 6.4<br>6.5 |                  | f COTS Products ic Evaluation Criteria                                                    | 6-2<br>6-3 |

|    | 6.6        |                  | net Databus-Specific Evaluation Criteria                                                  | 6-3        |

|    |            | 6.6.1<br>6.6.2   | Ethernet-Based Aviation Databus<br>Evaluation Criteria                                    | 6-3<br>6-3 |

|    | 6.7        | Satisfy          | ying the Avionics Application Requirements                                                | 6-7        |

|    |            | 6.7.1            | Avionics Application Requirements                                                         | 6-7        |

|                   |                | 6.7.2 Real-Time Communication Framework Requirements                                                                                    | 6-9  |

|-------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|

| 7.                | A PRO          | 7-1                                                                                                                                     |      |

|                   | 7.1            | Approach                                                                                                                                | 7-1  |

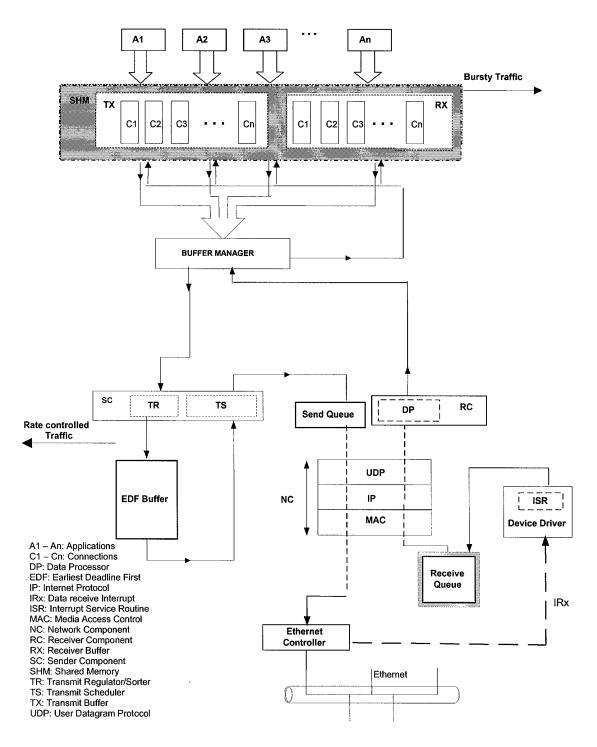

|                   | 7.2            | Components of the Communication Subsystem                                                                                               | 7-2  |

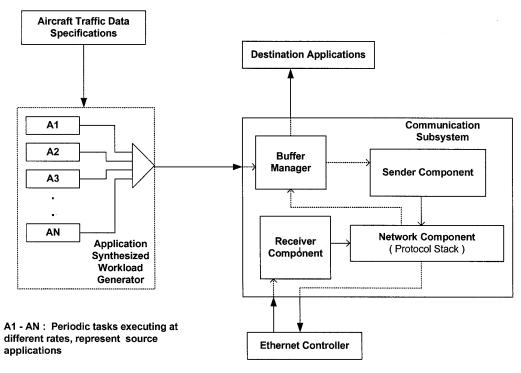

|                   |                | 7.2.1 Workload Generator                                                                                                                | 7-2  |

|                   |                | 7.2.2 Buffer Manager                                                                                                                    | 7-3  |

|                   |                | 7.2.3 Sender Component                                                                                                                  | 7-3  |

|                   |                | 7.2.4 Network Component                                                                                                                 | 7-3  |

|                   |                | 7.2.5 Receiver Component                                                                                                                | 7-4  |

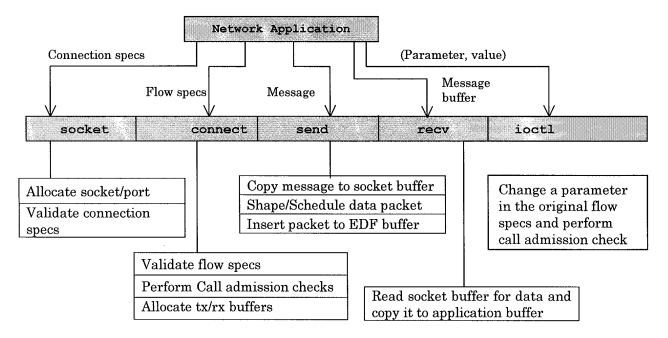

|                   | 7.3            | Quality of Service Specifications                                                                                                       | 7-4  |

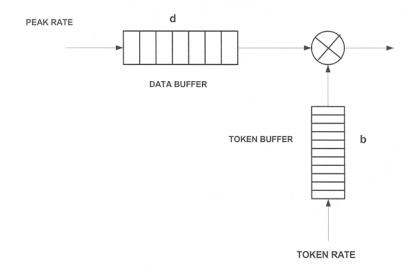

|                   | 7.4            | Traffic Regulator                                                                                                                       | 7-5  |

|                   | 7.5            | Packet Scheduler                                                                                                                        | 7-7  |

|                   | 7.6            | Network Component                                                                                                                       | 7-8  |

|                   | 7.7            | Data Flow in Communication Subsystem                                                                                                    | 7-9  |

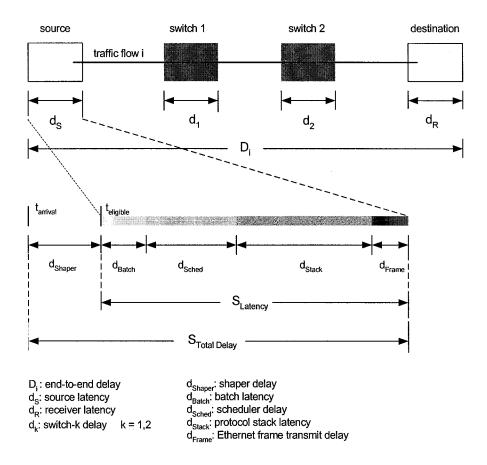

|                   | 7.8            | End-to-End Message Delay                                                                                                                | 7-9  |

|                   | 7.9            | Testing of the Prototype Communication Subsystem                                                                                        | 7-13 |

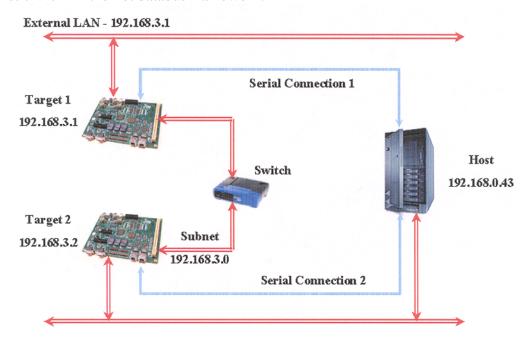

|                   |                | 7.9.1 Testing Environment                                                                                                               | 7-13 |

|                   |                | 7.9.2 Test Cases                                                                                                                        | 7-15 |

|                   | 7.10           | Results                                                                                                                                 | 7-17 |

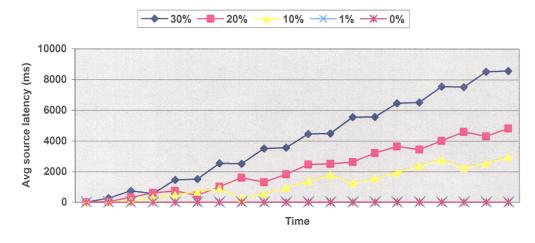

|                   |                | 7.10.1 Source Latency Analysis                                                                                                          | 7-18 |

|                   |                | 7.10.2 Guaranteed Service Validation                                                                                                    | 7-19 |

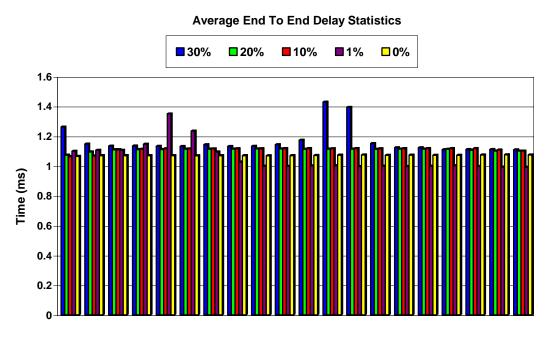

|                   |                | 7.10.3 End-to-End Delay Analysis                                                                                                        | 7-24 |

| 8. SUMMARY AND FU |                | MARY AND FUTURE WORK                                                                                                                    | 8-1  |

|                   | 8.1            | Summary                                                                                                                                 | 8-1  |

|                   | 8.2            | Future Work                                                                                                                             | 8-3  |

|                   | 0.2            |                                                                                                                                         |      |

| 9.                | REFERENCES 9-1 |                                                                                                                                         | 9-1  |

| 10.               | RELA           | RELATED DOCUMENTATION 10                                                                                                                |      |

| 11.               | GLOS           | SARY                                                                                                                                    | 11-1 |

| APPE              | NDICE          | S                                                                                                                                       |      |

| B-<br>C-          | —Detail        | ts of the Traffic Analysis ed Design of the Communication Subsystem fuction to Output-Queued and Input-Queued Switch Architectures Plan |      |

# LIST OF FIGURES

| Figure | 2                                                                                      | Page |

|--------|----------------------------------------------------------------------------------------|------|

| 2-1    | Communication Architecture in Ethernet-Based Aviation Databus System                   | 2-1  |

| 2-2    | End-Host System Architecture                                                           | 2-2  |

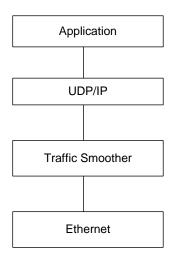

| 4-1    | Role of the Traffic Smoother in the Communication Architecture                         | 4-10 |

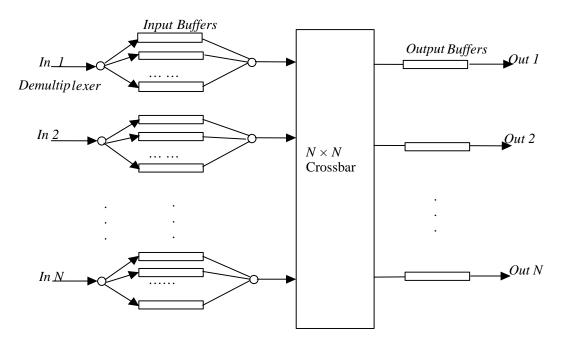

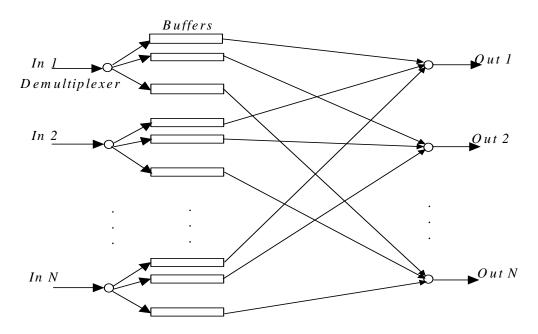

| 5-1    | Virtual Output-Queued Switching Architecture                                           | 5-9  |

| 5-2    | A Parallel Switch Structure—POQ                                                        | 5-10 |

| 7-1    | Interconnection Diagram—Communication Subsystem                                        | 7-2  |

| 7-2    | User-Level Socket Library                                                              | 7-3  |

| 7-3    | The Token Bucket Model                                                                 | 7-6  |

| 7-4    | Connection Descriptor and Token Bucket Shaper Structures                               | 7-6  |

| 7-5    | Data Flow Diagram—Communication Subsystem                                              | 7-10 |

| 7-6    | End-to-End Delay Model                                                                 | 7-11 |

| 7-7    | Test Bed for the Subsystem Evaluation                                                  | 7-13 |

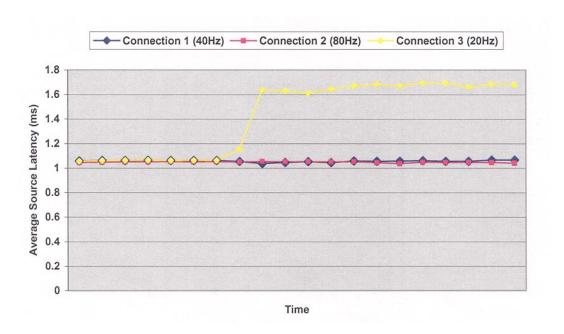

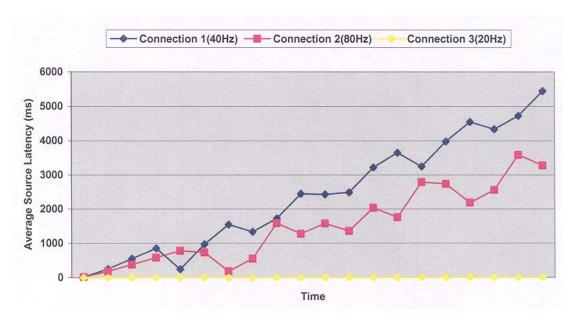

| 7-8    | Average Source Latency—Various Scale Factors                                           | 7-18 |

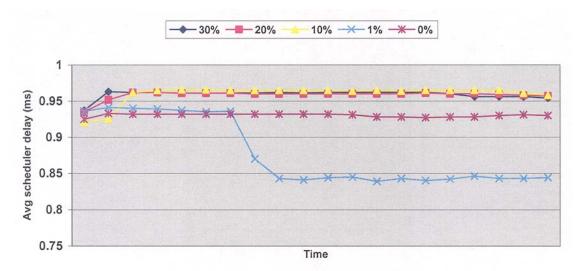

| 7-9    | Average Scheduler Delay—Various Scale Factors                                          | 7-19 |

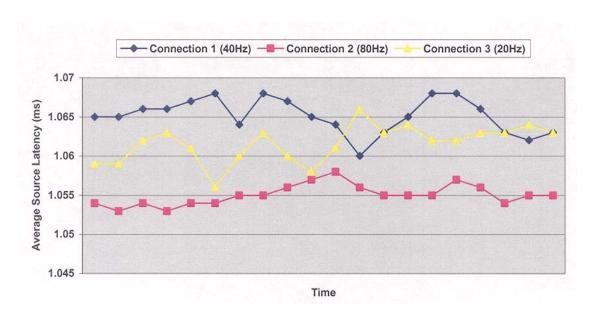

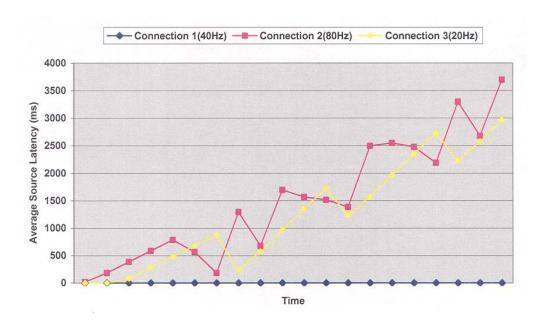

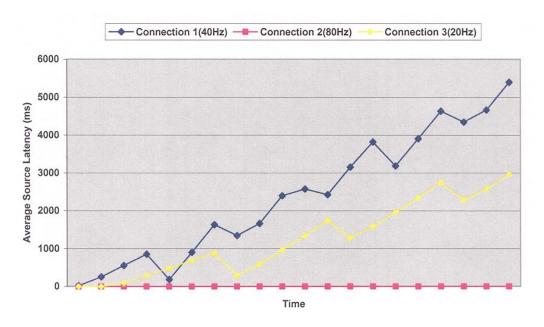

| 7-10   | Guaranteed Service Validation—Normal Flows                                             | 7-20 |

| 7-11   | Guaranteed Service Validation—Variation 1 (10% Scale Factor)                           | 7-20 |

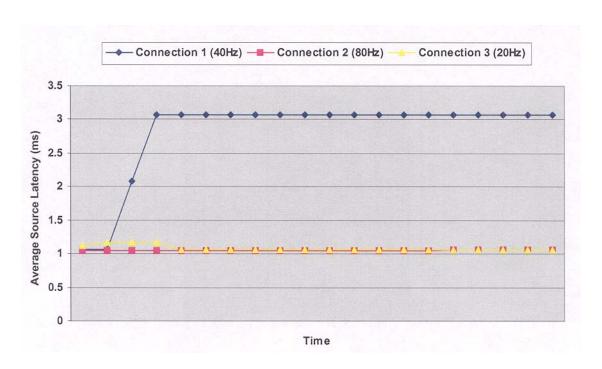

| 7-12   | Guaranteed Service Validation—Variation 2 (10% Scale Factor)                           | 7-21 |

| 7-13   | Guaranteed Service Validation—Variation 3 (10% Scale Factor)                           | 7-21 |

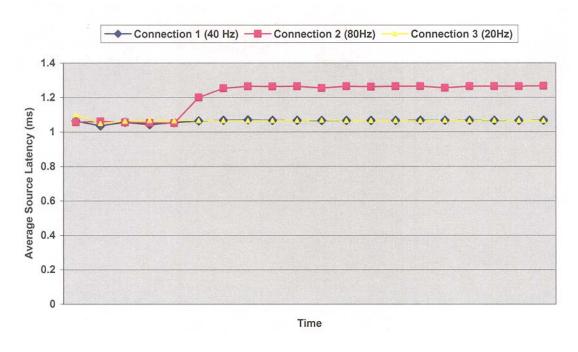

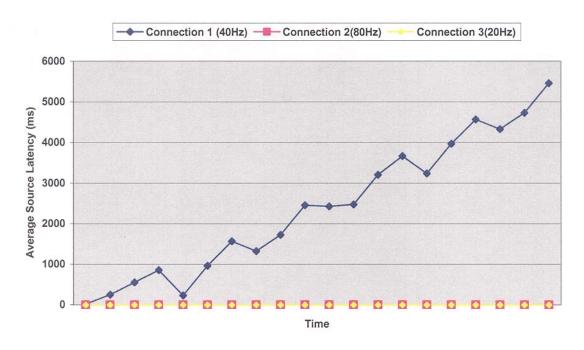

| 7-14   | Guaranteed Service Validation—Variation 1 (50% Scale Factor)                           | 7-22 |

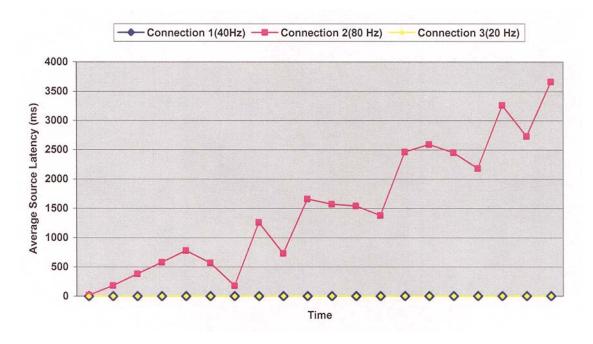

| 7-15   | Guaranteed Service Validation—Variation 2 (50% Scale Factor)                           | 7-22 |

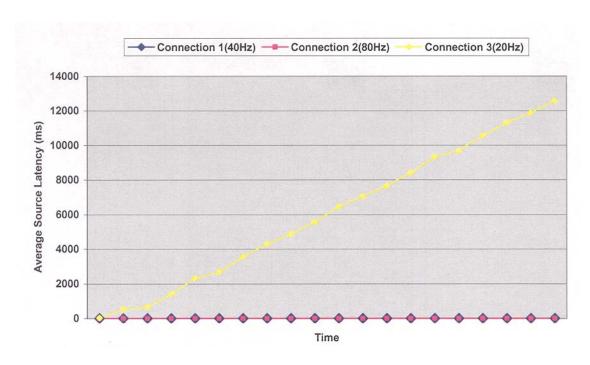

| 7-16   | Guaranteed Service Validation—Variation 3 (50% Scale Factor)                           | 7-23 |

| 7-17   | Guaranteed Service Validation—Variation 1 (Two Flow Violations in Connections 1 and 2) | 7-23 |

| 7-18 | Guaranteed Service Validation—Variation 2 (Two Flow Violations in Connections 2 and 3) | 7-24 |

|------|----------------------------------------------------------------------------------------|------|

| 7-19 | Guaranteed Service Validation—Variation 3 (Two Flow Violations in Connections 1 and 3) | 7-24 |

| 7-20 | Average End-to-End Delay—Various Scale Factors                                         | 7-25 |

# LIST OF TABLES

| Table |                                                             | Page |

|-------|-------------------------------------------------------------|------|

| 5-1   | Network Node Performance Estimation Theorems                | 5-3  |

| 5-2   | Comparison of Several Work-Conserving Disciplines           | 5-4  |

| 5-3   | Scheduling Order in a Frame                                 | 5-5  |

| 6-1   | Generic vs Application-Specific Databus Evaluation Criteria | 6-3  |

| 7-1   | Flow Specifications                                         | 7-18 |

## LIST OF ACRONYMS AND SYMBOLS

$d_{ij}$  Delay experienced by session *i* passing server *j* for D-EDD policy

$h(\alpha, \beta)$  The supremum of all values of  $\delta(s)$ , where  $\delta(s)$  is defined as  $\delta(s) = \inf \{ \tau \ge 0 \ \alpha(s) \}$

$\leq \beta(s+\tau)$

ADS-B Automatic Dependent Surveillance-Broadcast

API Application Programming Interface

ARP Address Resolution Protocol

CAC Call admission controller

CAST Certification Authorities Software Team

CIOQ Combined Input Output Queuing

CM Configuration management

COTS Commercial off-the-shelf

CPU Central Processing Unit

CSMA/CD Carrier Sense Multiple Access with Collision Detection

D-EDD Delay Earliest Due Data

DEOS Digital engine operating system

DMA Direct memory access

EC Evaluation criteria

EDF-RR Earliest deadline first-round robin

EFIS Electronic flight instrument system

FAA Federal Aviation Administration.

FANS Future Air Navigation System

FCFS First-come, first-served

FIFO First-in, first-out

FMCS Flight Management Computer System

GPS Generalized Processor Sharing

H-EDF-RR Hierarchical - Earliest Deadline First - Round Robin

HOL Head of Line

IEEE Institute of Electrical and Electronic Engineers

I/O Input/output

IP Internet protocol

IPC Interprocess communication

IQ Input queue

ISA Industry standard architecture

ISR Interrupt service routine

LAN Local Area Network

ms Millisecond

MAC Media Access Control

Mbps Mega bits per second

MII Medium Independent Interface

MTU Maximum transmission unit

NIC Network interface card

NP-EDF Non-pre-emptive earliest deadline first

OSI Open system interconnection

OQ Output queue

PCI Peripheral Component Interconnect

PHY Physical Layer

POQ Parellel output queued

QoS Quality of Service

RCS Rate-controlled services

RETHER Real-time ETHERnet

RFC Request For Comment

RR Round Robin

RTCA (formerly Radio Technical Commission for Aeronautics)

RTOS Real-Time Operating System

SCFQ Self-Clocked Fair Queuing

TCP Transmission Control Protocol

UDP User Datagram Protocol

VC Virtual Clock

VOQ Virtual output queued

VLSI Very large-scale integration

WFQ Weighted fair queuing

WF<sup>2</sup>Q Worst-case fair-weighted fair queuing

WS Wide-Sense

#### **EXECUTIVE SUMMARY**

Given that safety-critical real-time systems require deterministic behaviors in their communication operations, specialized communication networks have been used in the areas of avionics, defense, and space applications. This type of communication network is usually expensive, has a nominal bandwidth and complex wiring configurations, and has limited engineering support. On the other hand, with the advent of higher-performance computing and communication systems, aircraft will have the capability to process an unprecedented amount of information pertaining to performance, safety, and efficiency. Flight instruments will be integrated to share information and to cooperate with each other. It is inevitable that a high-speed and versatile network infrastructure will be required in the next generation of aircraft.

One commercial off-the-shelf technology, Ethernet, is seen as potentially attractive in avionics systems due to its high bandwidth, low wire counts, and low cost. It has been used in the Boeing 777 to transmit non-flight-critical data and in the Boeing 767ER within a flight-critical display system. However, there are many safety concerns when Ethernet is applied to flight-critical systems. The inherent nature of the Ethernet protocols can easily result in nondeterministic behavior and interference. These are significant technical hurdles that must be overcome before Ethernet will be a viable candidate as an aviation databus technology.

Ethernet was not designed to carry time-critical data. It is inherently nondeterministic in nature, and this is a factor that undermines its use in a time-critical system such as an avionics network. The nondeterminism in Ethernet is due to its use of the carrier sense multiple access with collision detection protocol for resolving bus contentions. Even in the presence of a collision-free environment for data transfer, one cannot guarantee that a data packet will be delivered on time. This is due to the fact that traffic in a real-time system tends to be bursty at times, and this burstiness can lead to buffer overflows both at the source (the transmit and receive buffers maintained by the Ethernet controller) and at the intermediate nodes, leading to packet loss. Therefore, the standard Ethernet will have to be supplemented with additional solutions to overcome this nondeterminism.

In this report, safety and certification issues of Ethernet-based aviation databuses are summarized. Initially, the report focuses on the issues of deterministic operations of Ethernet controller, device drivers, and communication stack, and possible solutions to avoid any adverse effects. A brief analysis of the traffic generated by a typical avionics system comprised of several avionics modules and applications is presented. This traffic analysis result can be used to estimate the amount of traffic generated by avionics applications and their properties. Then determinism in the communication system is discussed, and focus is placed upon the various hardware and software factors that cause nondeterminism in the end-node, including topics such as the use of Peripheral Components Interconnect-Direct Memory Access Ethernet controllers and the communication protocol stack. The report discusses issues concerned with the evaluation criteria for the qualification of Ethernet-based databuses. Several criteria are studied in detail to consider certifiability of future avionics databuses. With the intent to be more specific for the Ethernet-based aviation databuses, focus is placed upon four criteria: safety, data integrity, performance, and configuration management. Finally, a communication subsystem to support deterministic data delivery in Ethernet is illustrated. Using this prototype design as an example, the specific avionics requirements that can be satisfied are described, and a list of test

cases is provided. The example implementation is validated through the measurements of delay parameters, such as the source and receiver latency and the end-to-end delay for a mix of conforming and nonconforming traffic flows. The results of the performance evaluation show that real-time, deterministic support can be provided on an Ethernet-based databus without any changes to the underlying protocols or the hardware.

## 1. INTRODUCTION.

In the 21<sup>st</sup> century, advancements in data processing are resulting in higher bandwidth requirements. The speeds required are exceeding 10 megabits per second (Mbps) and the standard that is now being considered is one for 100 Mbps. Aviation is also moving from the use of low-bandwidth data to high-bandwidth data. Next-generation warning systems, for example, may want to combine map and air traffic data, terrain information, weather radar returns, information on man-made obstacles, and imagery on the airport environment, and finally fuse this information into single three-dimensional representation. The need for speedier communication to handle future growth requirements of avionic applications, such as the automatic dependent surveillance-broadcast (ADS-B) and Future Air Navigation System (FANS) warrant a move towards the use of a high-bandwidth databus as the communication medium in aircraft. Ethernet provides such a bandwidth and is being considered by aircraft and avionics manufacturers for current and future technologies. This report will consider its benefits and its safety and certification concerns. Potential solutions to these concerns will be presented and As a two-phase research effort, the first phase focused on evaluating several approaches, while in the second phase, these approaches were implemented and results analyzed.

## 1.1 A BRIEF OVERVIEW OF ETHERNET.

Ethernet was developed at Xerox in 1973 as a part of a research program on personal workstations and distributed systems [1]. Ethernet is a simple or branching bus-like network that uses low-loss coaxial cable linked by repeaters. It has a carrier sense, multiple access with collision detection (CSMA/CD) network classification. The most common way of carrying out the CSMA/CD communications is by broadcasting packets of data on a cable that is accessible to all the stations on the network. All stations are continually listening to the cable for packets that are addressed to them. To avoid packet collision, Ethernet implements three mechanisms: (1) carrier sensing, (2) collision detection, and (3) back off [1]. In carrier sensing, the interface hardware at each station listens for the existence of a signal in the cable. For collision detection, the sending station also listens on its input port to make sure that the message sent and received is the same. Back off occurs when a collision is detected and a jamming signal is sent. Back off is the process of waiting for a period of time before retransmitting the message [1].

The standard for Ethernet is Institute of Electrical and Electronic Engineers (IEEE) 802.3. There have been three major standardization efforts with the IEEE 802.3 standard. The 1990 version operated at a maximum of 10 Mbps and is commonly known as 10BaseT. The 1995 version operated at a maximum of 100 Mbps and is commonly referred to as 100BaseT [2]. In 1998, the Gigabit Ethernet was standardized. It operates at a maximum of 1 gigabit per second. The gigabit Ethernet is compatible with the slower Ethernets [3].

As mentioned earlier, Ethernet uses a broadcast delivery mechanism in which each data packet transmitted on the physical medium is received by all stations. It is also possible, however, to transmit data packets to a single station or to a subset of the stations on the network. When a data packet is sent to a single station on the network, the packet is said to be unicast. When the data packet is sent to a subset (or a group) of the stations on the network, it is said to be multicast. Broadcasting is basically a subset of multicasting.

# 1.2 WHY ETHERNET IS BEING PROPOSED FOR USE ON AIRCRAFT.

Ethernet is attractive in the avionics world. It promises to accommodate future systems' bandwidth demands, increase flexibility in avionics design and procurement, and reduce aircraft wire counts, thus lowering aircraft weight and operating costs. The use of Ethernet technology translates into greater flexibility in avionics architecture design and lower aircraft construction and operational costs. The most significant advantage of Ethernet (especially the 100-Mbps Ethernet) is its ability to allow for aircraft systems' bandwidth growth. Another attraction of Ethernet is its promise to free avionics data transfer in integrated avionics systems from the logistical limitations of a backplane bus of the special-purpose communications bus, linking computing modules inside of a physical enclosure. So in the future, Ethernet will likely replace the backplane bus for at least some aircraft.

## 1.3 WHY THIS RESEARCH IS NEEDED.

Avionics Ethernets need to guarantee and control bandwidth allocation to users on the network and ensure that the right data arrives at the right destination at the right time. There will be some extra electrical requirements on the cable, which also need to be considered to support the higher frequencies [4]. There are many safety concerns, however, when Ethernet is applied to flight-critical systems. The inherent nature of the Ethernet protocols can easily result in nondeterministic behavior. This and the electrical requirements together form significant technical hurdles that must be overcome before Ethernet will be a viable candidate as an aviation databus. This report focuses on the safety concerns of Ethernet-based aviation databuses.

## 1.4 AN OVERVIEW OF THIS RESEARCH PROJECT.

The purpose of this research project was to provide a comprehensive investigation of the safety and certification issues of Ethernet-based aviation databuses. The goal is to address the nondeterminism of Ethernet and identify mechanisms to incorporate determinism into the network. To this end, design and test approaches of assuring reliable, accurate, and real-time communication services using commercial off-the-shelf (COTS) Ethernet hardware and software methods were examined. Through test experiments and model analyses of real-life avionics applications, an improved understanding of the potential safety issues was gained and enlightened guidance relative to network structures and operations is provided. Collaborative relationships with standards working groups, the aerospace industry, and regulatory agencies were established. Through this process, the relevant concerns are being discussed and addressed, and an industrywide effort to define a safe Ethernet-based aviation databus network has been initiated by industry.

The principal results of this research were twofold: (1) a solution to overcome the nondeterminism in Ethernet was found to be the use of a switched Ethernet topology, along with traffic regulation, bandwidth restriction (guarantee and control of bandwidth allocation), and call admission control and (2) Ethernet databus evaluation criteria were found within the categories of safety, data integrity, performance, and continued airworthiness. The report can be used by the certification specialist for Ethernet databus qualification during the certification process. Also, the report can be provided to the designer as a reference for system design and development.

This project was divided into two phases. Phase one addressed the theoretical background and a review of several technical concerns and approaches carried out. Phase 2 addressed actual implementation and testing of the proposed solution of phase 1. It also addressed the safety, certification, and databus evaluation issues.

It should be noted that the Federal Aviation Administration (FAA) is sponsoring this research effort; however, the results of the research do not constitute FAA policy or guidance. This research is intended to explore the safety and certification concerns and consider potential solutions. However, actual implementation of these potential solutions on real aviation projects should be coordinated with the certification authorities, as with any certification project.

As with any hardware and software components, the safety process of using Ethernet as an aviation databus began with an aircraft-level assessment of functions and hazards (using the SAE/ARP-4761 approach [5]). The guidelines for development, including RTCA/DO-254 for complex hardware and RTCA/DO-178B [6] for software were followed. In addition, several fundamental issues, including scheduling, safety and fault-tolerance, were examined carefully since Ethernet networks are designed for commercial non-safety-critical applications. To study the safety features, the characteristics of Ethernet protocols were investigated in bus and switched configuration, COTS Ethernet Media Access Control (MAC) silicon, network interface cards (NIC), and switches (specially regarding deterministic transmission-reception operations, temporal and spatial protection, and real-time guarantees).

Also, the issues related to the test strategy of Ethernet-based aviation databuses were investigated. A workload generator, which synthesizes traffic load profiles from avionics applications, was developed as part of this test strategy. Instead of using real airborne instruments, the communication specification of several real-life avionics applications, including autopilot, electronic flight instrument system (EFIS), flight management computer system (FMCS), and communication radio, were analyzed to establish a profile of message characteristics. This approach allows scaling the communication requirements and adjusting the traffic loads based on anticipated applications. The synthesized workload can then be supplied to Ethernet-based aviation databuses under various workload parameters. The other tools, which provide fault injection and performance measurement, are also useful for the certification and development phases.

As stated previously, through this project, it is endeavored to provide a solution to overcome nondeterminism in Ethernet. More precisely, efforts have concentrated on the following:

- Analysis of systemwide and nodewise traffic generation to understand the load on the system (as a whole) and the traffic generation patterns on a per node basis.

- Study of the factors contributing to nondeterminism in the nodes as well as in the Ethernet medium used by the nodes for communication.

- Study of schemes (both hardware and software) through which determinism could be incorporated both in individual nodes (end points of the network) and the intermediary elements (switches) of the network.

When determinism is discussed in this report, it is meant in terms of the bounds that can be achieved for such parameters that affect real-time traffic, such as delay and jitter. To obtain performance bounds, a static approach is considered with which network traffic is smoothed and regulated. Thus, the worst-case behavior and resource requirements can be predicted.

Phase 1 of this research was a concept study phase in which the possibilities of applying various policies (e.g., scheduling of real-time communication packets) in the Ethernet as it exists today were studied. Several approaches (both hardware and software) to introduce determinism in Ethernet were identified and analyzed. Below is a summary of the tasks carried out towards the development of a deterministic Ethernet framework (the rationale for each will be discussed in this report).

- The communication subsystem (a software process) residing on each node in the network was developed. All traffic sent by the concerned avionic application and intended for another similar application passes through this communication subsystem. This subsystem bounds the delay experienced by a data packet at the end-nodes. Thus, it addresses the issue of incorporating determinism at the individual nodes of the network.

- A new packet-scheduling algorithm, Earliest Deadline First-Round Robin (EDF-RR), was developed for distributed real-time applications such as flight-critical applications. According to the analysis of the delay bounds and buffer requirements obtained in the appropriate switch architecture, EDF-RR is suitable for real-time communication.

- A new switching architecture called the Parallel Switching Architecture along with an extension of the EDF-RR algorithm (Hierarchical-EDF-RR) was developed. It is a solution to integrate unicast and multicast traffic scheduling in packet-switching networks with guaranteed performance.

- Investigated the factors affecting nondeterminism in the host (node) (e.g., in the network stack, Ethernet controller design, etc.) to minimize the overheads to real-time communication caused by those factors.

The impetus in phase 2 was on implementing these approaches, testing the design with appropriate data with a view to analyze the results, and defining the evaluation criteria for the qualification of Ethernet-based aviation databuses. The following is a list of tasks carried out in phase 2:

- Generic evaluation criteria were developed to certify future avionics databuses. Eight generic evaluation criteria are described that are independent of the design and implementation of any databus.

- Ethernet databus-specific evaluation criteria were developed to certify future Ethernet-based aviation databuses. These are the subset of the above generic evaluation criteria.

- A detailed timing analysis of the communication subsystem was performed to obtain precisely the execution budgets of the individual threads of the subsystem. Their effect on the timely delivery of data in the network was determined and the approaches for adequate resource reservation throughout the system was devised.

- A thorough analysis of some of the mechanisms used in the communication subsystem is worked out in much greater detail. An example mechanism includes one to handle incoming connection requests (Call Admission Control) and handling exceptions in the system behavior.

- A test bed was developed and used to disclose the characteristics of Ethernet-based databuses. The suite includes tools for real-time traffic generation and performance measurement. Sample test benchmarks were constructed based on practical applications.

A close collaboration with the FAA research team was extremely helpful in identifying the acceptance criteria and in defining the functions of the test suite.

## 1.5 REPORT ORGANIZATION.

This report is organized as follows:

- Section 2 gives a brief overview of the system architecture based on Ethernet databus.

- Section 3 provides the brief analysis of the traffic generated by a typical avionics system comprised of several avionics modules and applications. This study was done to estimate the amount of traffic generated by avionics applications and to understand the traffic patterns (such as data rates, packet length distributions, and burstiness). The effect of unicasting and multicasting in such environment was also identified.

- Section 4 describes the determinism in the communication system and focuses on the various hardware and software factors that cause nondeterminism in the end-node, including topics such as the use of Peripheral Components Interconnect-Direct Memory Access (PCI-DMA)-based Ethernet controllers and the communication protocol stack.

- Section 5 discusses the deterministic data communication and quality of service (QoS)-related problems in packet-switching networks. A solution is proposed in terms of switch architecture and service discipline to integrate unicast and multicast traffic scheduling with guaranteed performance.

- Section 6 describes the general acceptance criteria for the qualification of future avionics databuses. It lists eight criteria required to evaluate any generic aviation databus. Among these evaluation criteria, four are defined to be databus-specific. Hence, these criteria are described in detail for Ethernet-based aviation databuses. These evaluation criteria are used to describe how the avionics application requirements can be satisfied.

- Section 7 describes the entire structure and model of an Ethernet-based aviation databus. It explains the proposed communication subsystem model design, data flow within the system, and implementation details of each component of the subsystem. The test environment setup and test plan is also provided. Finally, the results of the implementation are described. These results are evaluated by validating the performance of each component of the communication subsystem.

- Section 8 concludes the report by summarizing major achievements of the project and lists future research activities.

- Section 9 provides a list of references used throughout the research project.

- Section 10 is a list of related documentation.

- Section 11 is a glossary of key terms used in this report.

- Appendix A provides detailed analysis of the traffic generated during normal operation of the aircraft. Appendix B describes the detailed design of prototype communication subsystem. Appendix C gives an overview of output-queued and input-queued switches. Appendix D tabulates the test plan, described in section 7, in detail.

# 1.6 FOCUS FOR READERS.

This report provides information for a variety of readers. Two of the targeted reader groups are described below, with a suggested approach for reading this report.

## 1.6.1 Readers Concerned With Ethernet Databus Qualification.

The readers, concerned about the qualification of an aviation databus, should understand the certification requirements of the aviation databus. The general acceptance criteria, and more specifically, acceptance criteria defined for the Ethernet-based aviation databus (described in section 6) will help such readers to evaluate the databus for avionics requirements. The avionics application requirements and real-time communication framework requirements listed in section 6 will help these readers to validate the databus solution to be qualified. Before that, browsing through sections 1 and 4 will also be helpful for these readers to understand the basic Ethernet-based databus system model and the issues related to deterministic operations in Ethernet databus.

# 1.6.2 Readers Concerned With Ethernet Databus Development.

The software architects, designers, and researchers, developing a solution for an Ethernet-based real-time communication framework, should read sections 2 and 4 to understand the real-time communication requirements and nondeterministic factors involved in the Ethernet-based communication framework. The analysis of deterministic data communication described in section 5 and the prototype design, implementation and results (defined in section 7) will help to explore the possible solutions. If the Ethernet-based, real-time communication framework to be developed is within the avionics application domain, then traffic analysis of avionics data provided in section 3 and appendix A will be insightful.

### 2. ETHERNET-BASED DATABUS SYSTEM MODEL.

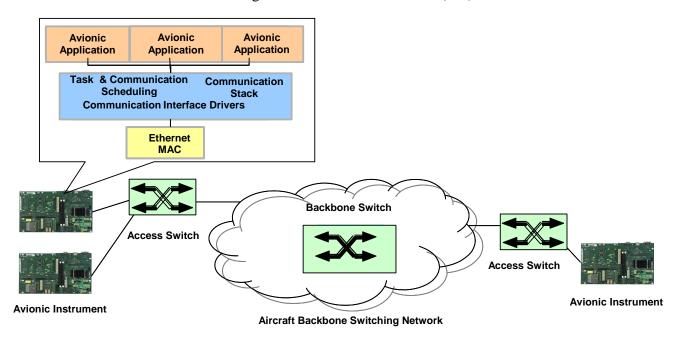

This section gives an overview of the architecture of an Ethernet-based aviation databus model. Figure 2-1 shows the entire setup with the individual nodes connected to the Ethernet network and the intermediate switches linking different collision domains (bus).

FIGURE 2-1. COMMUNICATION ARCHITECTURE IN ETHERNET-BASED AVIATION DATABUS SYSTEM

As mentioned in the previous section, Ethernet can be made more deterministic by making the individual components in such a system deterministic by themselves. The components referred to here are the end-hosts (the avionic instrument is shown in figure 2-1) and the switches. The end-host system architecture and related topics are presented in this section, section 4, and section 7, whereas section 5 is devoted to switch architectures and its related topics.

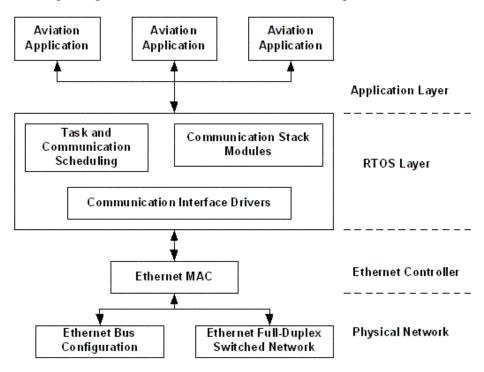

An end-host (node) of the Ethernet-based aviation databus consists of four parts (or layers), as shown in figure 2-2: a physical Ethernet network, an Ethernet MAC silicon or NIC, communication software and real-time operating system (RTOS) scheduling components, and an integration approach to merge communication services with high-level applications. Each layer is briefly described below:

- Application Layer. This is the layer where avionics applications (such as autopilot, EFIS, and FMCS) execute. These applications are communication intensive and use the aviation databus to communicate with each other. The destination application can be located either on the same host or on a remote host also connected to the same network.

- RTOS Layer. This layer provides the resource management facilities, the protocol stack, the necessary network services (e.g., sockets) used by the upper layers for invoking data transmission, and the basic interprocess communication (IPC) mechanisms, such as

mailboxes and shared memory used by the applications. The applications are scheduled by RTOS to run on the processor. The candidate RTOSs for the purpose of this research include Wind River System's VxWorks<sup>®</sup> and Honeywell's DEOS<sup>©</sup>. <sup>1</sup>

- Ethernet MAC Layer. The Ethernet MAC layer is nothing but the low-level device driver of the NIC or the Ethernet Controller. It implements first-in, first-out (FIFO) buffers for storing and forwarding packets to the underlying bus. The MAC layer is independent of the interconnection mechanism used in the network in the sense that its main functionality is to handle data packet arrivals from the upper layers and hand them to the physical network and vice versa irrespective of the whether the underlying network is a switched network or just a bus topology.

- Physical Network Layer. The Physical network can be bus based or switch based. In a bus-based system, a single bus connects all the nodes in the network, and data transmission can be carried out in only one direction at a time by any one node. The data transfer mode is therefore half duplex. Arbitration mechanisms are needed to avoid data collisions resulting from more than one node trying to access the bus at the same instant. Protocols such as the CSMA/CD are used for this purpose. The delay involved in transmitting is high in this case, since it involves waiting for bus access.

FIGURE 2-2. END-HOST SYSTEM ARCHITECTURE

\_

<sup>&</sup>lt;sup>1</sup> Digital Engine Operating System (DEOS) refers to Honeywell's RTOS for avionics applications.

In a switch-based system, separate conductors are used for sending and receiving data. In a fully switched network, Ethernet nodes only communicate with the switch and never directly with each other. Thus, they can forego the collision detection process and transmit at will. Hence, data transmission between the switch and the nodes takes place in a collision-free environment. This is called a full-duplex system since data can be transmitted in both directions simultaneously. This introduces more determinism into the system.

## 3. TRAFFIC ANALYSIS.

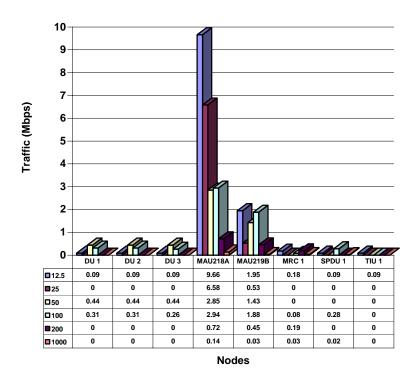

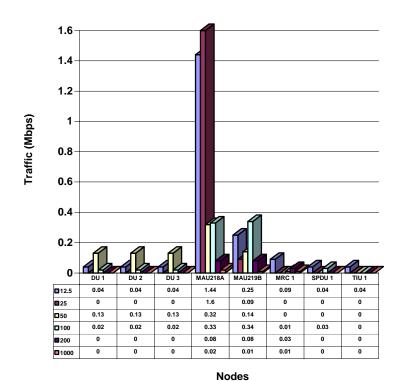

Given the Ethernet-based databus system model, it is necessary to understand the characteristics of data traffic in typical aviation applications. This section will provide statistical data extracted from the aircraft data specifications provided by Honeywell Laboratories Inc. (Phoenix, AZ). The results of this analysis will be used to determine the overall system load in terms of the amount of traffic generated and also to characterize traffic based on their rates of generation. This analysis can also be used to determine how much data is typically handled by any communication system on a per node basis.

## 3.1 OVERVIEW OF THE TRAFFIC ANALYSIS.

This section summarizes the traffic analysis carried out for a sample set of data reflecting information flow on the aircraft bus. The objectives of this traffic analysis were as follows:

- To find the raw traffic data generated with the basic information available at present without applying any of the other parameters such as the round-trip time and intrapacket delay, as is usually the case in any traffic analysis report.

- To find the effect of the use of the three main protocols, i.e., MAC, Internet Protocol (IP), and Transport Control Protocol (TCP), for data transmission in terms of the traffic generated by each due to the overheads on the basic Ethernet data frame.

- To find the effect of the use of multicasting in data transmission whenever possible and to compare resultant traffic generated when using a point-to-point versus a multipoint approach.

The information used as input to the traffic analyzer was comprised of several data fields in a spreadsheet format. A listing of those data fields is given below, along with a brief description of what each field stands for wherever necessary:

- Source Bus. The number of the bus used for data communication by the source and destination modules.

- Source Unit-Module. The source of data on the bus.

- Source Application. The specific application within the source unit-module that generated this data.

- Parameter Group. A logical name given to the data to be sent by the source.

- Dword Size. The size of the data to be sent (i.e., the parameter group) in double-word units (32 bit).

- Rate (ms). The frequency with which the source sends out this data on the bus in milliseconds.

- Consuming Unit-Module. The destination of the data on the bus.

• Consuming Application. The specific application within the destination unit-module that is the recipient of this data.

### 3.2 COMPUTATION ENVIRONMENT.

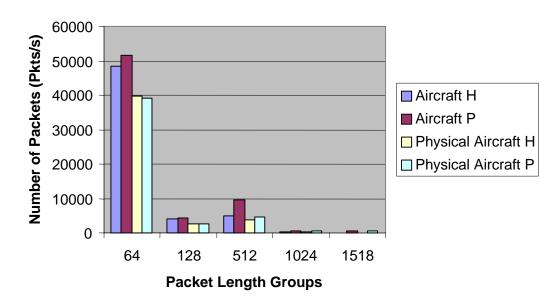

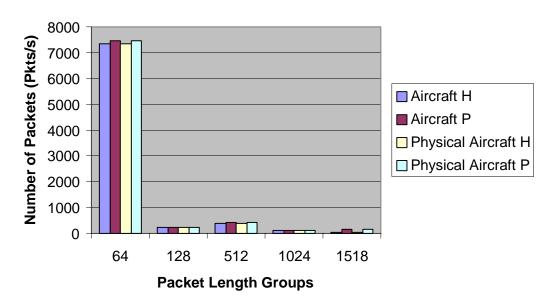

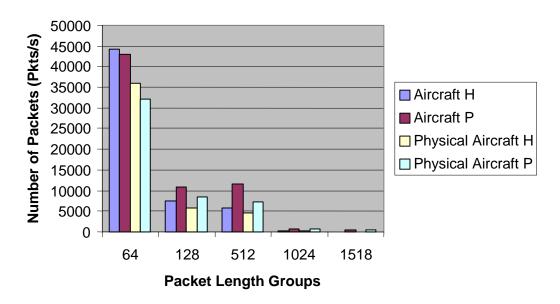

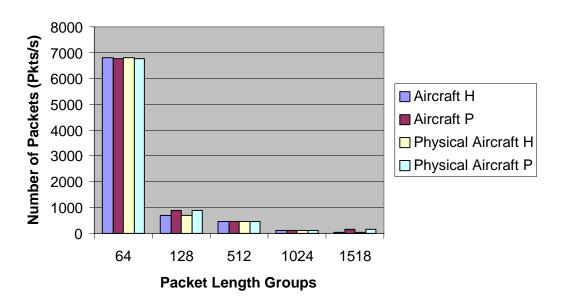

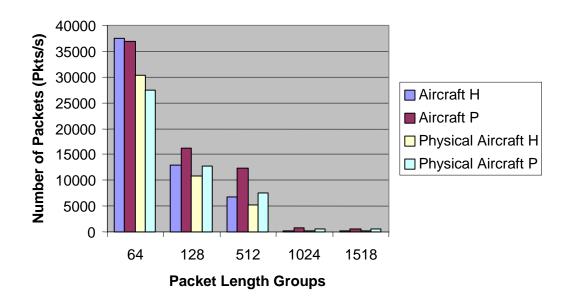

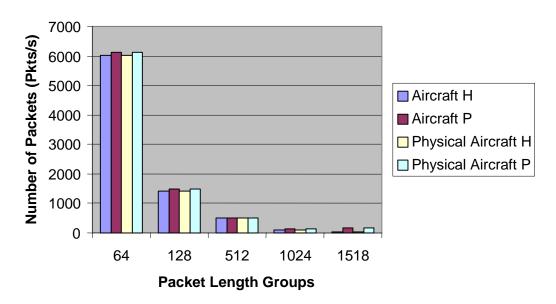

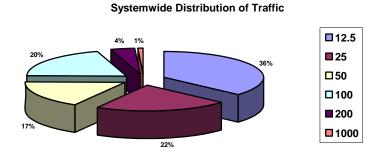

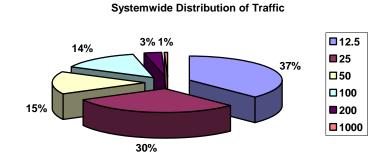

The analysis was carried out for four different types of aircraft data designated as Aircraft P, Aircraft H, Physical Aircraft P, and Physical Aircraft H. Here, Physical Aircraft and Aircraft actually represent the same aircraft. However, the Physical Aircraft data shows the movement of data between the physical modules/nodes in the system, whereas the Aircraft data shows the movement of data between the producing and consuming software applications allocated to the modules/nodes. Because the modules/nodes on these aircraft run an operating system with time and space partitioning, a module can run multiple applications, even if they are unrelated and are developed for different levels of assurance. This collocation of applications makes for less traffic at the device-to-device level than would be found in systems where these various applications must run on distinct hardware.

The traffic on each bus (of these dual-bus systems) was computed separately and an average was taken from the two. The bandwidth details of the Ethernet medium used was not taken into consideration since this analysis was done only to get an idea of the total load in the system without regard to the bandwidth available for that traffic. For purposes of computing the packet rate (i.e., the number of packets arriving on the bus in packets/second), the packet size was assumed to be fixed and was assumed to be equal to the minimum Ethernet packet size mainly because of the small data size for a majority of inputs. The traffic in terms of Mbps can be considered to be more accurate compared to that in packets/second for all practical purposes.

# 3.3 SUMMARY OF ANALYSIS RESULTS.

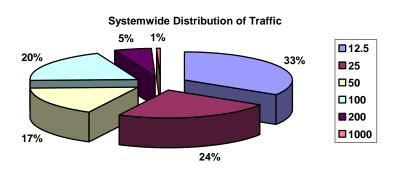

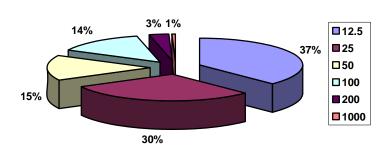

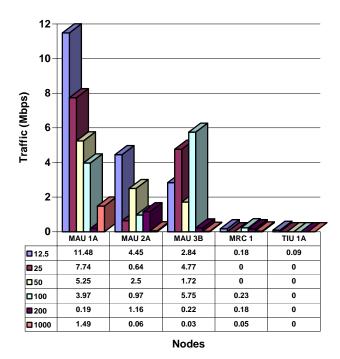

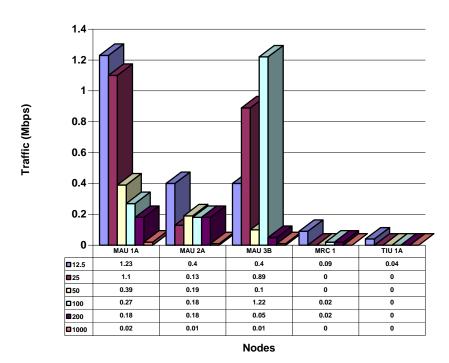

The results of the analysis are given in appendix A of this report and can be summarized as follows:

- By using multipoint communication (i.e., multicasting), there is a considerable reduction (almost 1/8) in the amount of traffic generated compared to using point-to-point communication. Thus, it would be a worthwhile exercise to explore the possibilities of using multicasting in the aircraft databus setup. If constrained to use a 10-Mbps Ethernet, one can make use of multicasting to satisfy the high demand for bandwidth.

- There is not much overhead in terms of the traffic generated irrespective of the different protocols (i.e., IP, TCP, and MAC) used. However, this analysis does not take into account additional bytes that form part of the IP options when considering the traffic generated for IP and TCP.

- The per node data generated is well within the bandwidth available in 10-Mbps Ethernet, and most of the data sent is usually very small, even though it is sent frequently. This kind of categorization of data can help to provide different services for data, which is of a minimal fixed size, and data that needs fragmentation and is of variable size.

## 4. DETERMINISM IN COMMUNICATION SYSTEM.

This section defines determinism in a real-time communication system. It also identifies factors resulting in the nondeterministic behavior of the software and hardware components on the end-host system. The end-host architecture specified in section 2 holds for the purpose of this analysis. Additionally, potential steps to mitigate the nondeterminism are mentioned where such steps are possible.

# 4.1 DETERMINISM.

Before listing the factors that affect deterministic data transmission and reception, let us define clearly what is meant by determinism. Determinism, at a network level, can be defined as the ability of the network to guarantee delivery of messages (data) to the nodes belonging to that network within a specified period of time. At the individual node level, determinism is used as a measure of the concerned system's ability to process an input in a time-predictable fashion. For this research project, determinism, as defined by the former, is considered, though determinism at both levels is equally important. Together they lead to a highly dependable system, especially in an environment such as in this project where the nodes represent the various avionics applications with the Ethernet acting as the medium of communication between them. In fact, in this scenario, the two forms of determinism are very strongly intertwined and each drives the other.

The factors that affect the deterministic transmission and reception of data on Ethernet are summarized below:

- The amount of bandwidth available on the network

- The number of nodes connected to the network

- The average rate of traffic flow through the network and its burstiness

- The protocols used for data communication and conflict resolution on the network

- The data transmission and reception rates of the individual nodes

- The interconnection hardware used

The remainder of section 4 addresses the issues related to determinism at the node level.

# 4.2 ANALYSIS OF NONDETERMINISM IN THE HOST—HARDWARE COMPONENTS.

Assuming a PCI bus-based hardware platform and a NIC, which is under the control of a host processor, the analysis of various delay factors is carried out. These delay factors are due to interrupt latency, the latency of PCI bus access and arbitration, memory read/write operations, and FIFO buffer.

PCI bus, a local bus standard developed by Intel, is widely used in modern computer systems and has become a dominant one. The main advantage that PCI has over other buses (e.g., Industry Standard Architecture (ISA)) is its enormous bus bandwidth. For instance, for a 32-bit PCI bus (PCI can also be implemented as 64 bits) that runs at a clock speed of 33 MHz, a throughput rate of up to 133 Mbps can be achieved. Also, PCI bus supports decoupling central processing unit (CPU) and peripheral buses as much as possible. DMA, a way to reduce the CPU involvement

in transferring large amounts of data between the main memory and input/output (I/O) devices, is often adopted in PCI bus systems. Therefore, it is not a surprise to see that these days Ethernet controllers have a PCI-DMA interface.

Even though it has a high throughput rate, the PCI bus was not initially developed to accommodate time-critical applications and does not guarantee high data transfer performance at all times. Industrial testing shows PCI bus performance is very complex and, consequently, hard to predict. Thus, in a real-time system where communication tasks are bound by PCI-DMA Ethernet, PCI bus is going to be the bottleneck of Ethernet NIC in terms of throughput and latency. PCI-DMA Ethernet controllers transmit and receive data frames by making use of interrupt mechanism, burst reading, and writing to PCI devices (DMA operations). These result in some nondeterministic features that are not suitable to real-time communications.

To ensure the deterministic communication performance of PCI-DMA Ethernet NIC, factors contributing to its nondeterminism should be carefully analyzed. These factors are explained in the sections below.

## 4.2.1 Interrupt Chaining Latency.

According to the PCI specification [7], "the system vendor (computer vendor) is free to combine the various interrupt signals from the PCI connector in anyway to connect them to the interrupt controller." Hence, a device driver may have much freedom to configure the device's interrupt routing to the host machine. This may inadvertently degrade the entire system performance, in light of delay and predictability, when multiple devices have interrupts associated with the same interrupt service routine (ISR) in the host machine. In other words, an interrupt chain is formed.

To illustrate the performance deterioration resulting from interrupt routing, consider a typical PCI/ISA combination design in which similar interrupt signal pins from various PCI connectors are connected (e.g., all the INTA#² pins are connected and all INTB# pins are connected) and directed to a programmable interrupt router. The router then routes the interrupt group to an existing ISA interrupt, which leads an interrupt chain. The flaw with interrupt chaining is an increase in interrupt latency, if a specific interrupt service routine does not stay at the head of the chain. The interrupt latency (the time elapsed from the time a device activates an interrupt to the time the corresponding interrupt service routine runs) varies, depending on where the interrupt service routine for the device is located in the chain. In the worst-case, when all the interrupts in the chain are invoked simultaneously, the latency of the last interrupt would be much longer than when it is invoked by itself. It is possible that the interrupt chain can be updated at run time. In other words, some interrupts in the chain may be disabled, some may be added to the chain, and some already in the chain, but disabled, may be enabled again. All of these can happen at system run time.

All the factors mentioned above contribute to the nondeterministic interrupt latency of PCI devices such as PCI-DMA Ethernet NIC. Even if only one interrupt is invoked in an interrupt chain (e.g., the last one in the chain) for reaching its associated interrupt service routine, the CPU would have to traverse the whole interrupt chain on every interrupt, wasting processing cycles.

$<sup>^2</sup>$  The notation INTA# represents a signal pin named INTA, which is active when low (i.e., negative logic).

This gives rise to an increase in interrupt latency. Because of long and unpredictable interrupt latencies, the use of PCI-DMA Ethernet NIC may cause nondeterminism in real-time systems.

## 4.2.2 Interrupt Latency From Lock and Demand Legacy DMA Modes.

Pre-emption is an important feature in real-time systems, which can improve system deterministic performance. When applying PCI-DMA Ethernet NIC in real-time applications, it is normally expected that DMA operations are capable of supporting pre-emption from other higher-priority transactions. However, DMA modes (such as those by PCI-DMA Ethernet controllers) do not permit pre-emption attempts by other bus masters. During DMA operation cycles, the CPU can go on executing some instructions in the pipeline or cache; but when I/O or main memory-addressing operations are encountered, the CPU will halt until the DMA cycle is accomplished. Since almost all interrupt service routines must perform at least one I/O operation to the bus (e.g., at a minimum, an end of interrupt command must be sent to the programmable interrupt controller), it is possible to prevent the ISR from completing any I/O until the legacy DMA transaction is done. As an example, with PCI-DMA Ethernet controller, suppose that the controller has received a frame and an interrupt is generated to inform the host machine of the coming frame, it is possible that the PCI bus is possessed by a DMA cycle of the transmit process, which cannot be pre-empted. Since the host can find out the frame's arrival only after the interrupt is returned, the receive process is postponed by the DMA cycle.

## 4.2.3 Interrupt Latency From Context Switching.

In modern operating systems, any interrupt response involves context switching between kernel mode and user mode. Depending on process scheduling and the interrupt management mechanism, there are some nondeterministic factors in context switching in terms of latency. For instance, in the Linux system, the work that the ISR should do is assigned to what is called a bottom half, which is scheduled to run at a later time. The duration from the time an interrupt is triggered to the time when the bottom half is executed could be quite large, since some urgent work might have to be completed before the bottom half is run and is thus nondeterministic.

## 4.2.4 Virtual Memory and Noncontiguous Buffers.

DMA devices reference only a block of contiguous physical address. However, the operating system and application programs reference virtual memory. For a DMA device to run with the virtual memory manager of an operating system, the driver software for the device must assume the responsibility of supervising the data location and managing the data transfer between physical and virtual memory. Before data can be transferred, the virtual memory manager must be instructed to map the data buffer from virtual memory to physical memory (page in). Sufficient physical memory must be available to contain the entire buffer. In addition, physical memory must be locked so that it is not moved to another memory location (for example, performing a page out to meet the memory needs of another operation), while the DMA is in progress.

A DMA operation command is issued by the application program, which references the buffer in virtual memory. A DMA device (the operation executor) references contiguous physical address. But a contiguous buffer in virtual memory cannot guarantee contiguity in the physical

memory. It is possible that a contiguous buffer in virtual memory consists of multiple distinct (noncontiguous) physical segments. In that case, it will take more than one DMA transaction to transmit the data in this virtual memory buffer. The time to transmit two virtual buffers of data of the same length may vary greatly. The driver has to know exactly the mapping from virtual memory buffer to the segments of contiguous physical memory. The data in a fixed buffer in virtual memory could be transferred through DMA operations in a large range of time intervals at different times due to paging on demand and physical memory fragmentation in some operating systems.

# 4.2.5 Latency From Non-Pre-Emptive DMA Mechanism.

When one DMA transaction is executing, another DMA request of an even higher priority than the executing one cannot be granted until the current transaction terminates because the bus arbiter normally does not use the pre-emption mechanism to assign bus-to-master devices. DMA cycles on the PCI bus are proportional to the sizes of the data to be transferred. The larger the block of data to be transferred, the more delay that could be introduced to a latter DMA request when the former one is executing. The scenario, for example, to be considered in Ethernet NIC, is how to coordinate the DMA priorities of transmit and receive. Obviously, transmit and receive DMA operations influence transaction latency to each other since they share PCI address and databuses.

## 4.2.6 Disparity Between the Half-Duplex PCI Bus and Full-Duplex Ethernet Controller.

Most computer bus standards, including PCI, support only half-duplex mode. All bus operations are serialized such that read and write, for example, cannot be executed in parallel. On the other hand, it is expected that the Ethernet controller will run in full-duplex mode for real-time communications, using separate queues for transmit and receive. In spite of the full-duplex operation of the controller, the PCI bus by which the host transmits and receives frames can only be possessed by one master device at a time. This is the essential reason why the PCI bus is the bottleneck for applying this type of controller in real-time applications.

## 4.2.7 The PCI Bus Arbitration Latency.

Arbitration latency is defined as the number of bus clock cycles it takes between a master's request of the bus and when the arbitra grants the bus to that master. This period is a function of the arbitration algorithm, the master's priority and whether or not any other masters are requesting access to the bus. Thus, the arbitration latency is implementation dependent, and thus nondeterministic.

# 4.2.8 Latency of PCI Burst Read/Write Process.

For zero wait (PCI has no waiting status once a transaction is issued), PCI devices such as those in most PCI-DMA Ethernet controllers, the latency of burst read/write is unpredictable. A read/write operation is composed of an address phase and multiple data phases.

$$T = T_a + n * T_d$$

where

T = time of a burst read/write  $T_a$  = time of an address phase n = size of data in one burst operation

$T_d$  = time of a data phase

This time T can vary, depending on  $T_d$  and n, thus resulting in nondeterminism.

The latencies and nondeterministic concerns mentioned in this section must be considered when designing the system and when choosing the Ethernet controller for use.

## 4.3 ANALYSIS OF NONDETERMINISM IN THE HOST—SOFTWARE COMPONENTS.

This section discusses only those protocols (network, Ethernet MAC, and transport layer) that are of concern in this project. Ethernet supports protocol multiplexing that allows an Ethernet to carry multiple distinct network layer protocols such as AppleTalk, Digital Equipment Corporation's network protocol suite (DECnet), IP, and Internetwork Packet Exchange. Upon receiving an Ethernet frame, a node must decide what protocol should accommodate the payload of the Ethernet frame by checking the frame's Ether Type field. In the case of IP, its Ether Type is 0x0800. The frame is then processed by upper layer protocols such as User Datagram Protocol/Transmission Control Protocol (UDP/TCP).

## 4.3.1 The CSMA/CD Protocol.

Ethernet uses a CSMA/CD mechanism to resolve contention in case of simultaneous data transmission. If two nodes transmit messages simultaneously, the messages collide and are destroyed (i.e., data is lost). The two transmitting nodes listen to the network to detect a message collision. If a collision is detected, the transmitting nodes wait a random length of time to retry transmission. The standard binary exponential back off algorithm determines this random length of time. The randomness of this waiting time essentially makes CSMA/CD nondeterministic.

Additionally, if 16 collisions are detected, the node stops transmitting and reports an error. To relate collisions to time delays, the blocking time of Ethernet is considered. The blocking time is defined as the time a message must wait to be sent, once a node is ready to send the message. It includes waiting time (while other nodes are sending messages) and the time needed to resend the message, if a collision occurs. If a message experiences n collisions (where  $n \le 16$ ), its blocking time can be

$$T_{block} = \sum T_k + T_{resid}$$

, (for  $k = 1$  to  $n$ )

Where  $T_{resid}$  denotes the residual time until the network is idle, and  $T_k$  is the random back off duration after the  $k^{th}$  collision. It is easy to see that  $T_{block}$  is not deterministic and may be unbounded due to the discarding of messages [8].

However, CSMA/CD is used only when the network topology is a bus-based configuration. In a full-duplex, fully switched topology, CSMA/CD is turned off; hence, it is a collision-free environment (i.e., There is a dedicated link, one for transmission and another for reception

between each node. Also, nodes are never directly connected to other nodes in the network, they are always connected through switches).

### 4.3.2 Internet Protocol/Address Resolution Protocol.

For IP to use Ethernet to communicate with an IP stack on another station, it must have a way to discover the destination MAC address. A table of neighbor IP addresses versus MAC addresses must be maintained for the sake of mapping from IP address to MAC address.

The IP suite has a protocol called Address Resolution Protocol (ARP) running directly over Ethernet without an IP head. ARP is used by IP end-stations to find neighbor MAC addresses with a certain IP address, and then the owner of that address will respond directly to the requester, if it gets the request. An ARP frame is a special Ethernet frame.