#### DOT/FAA/TC-16/40

Federal Aviation Administration William J. Hughes Technical Center Aviation Research Division Atlantic City International Airport New Jersey 08405

# Commercial Off-the-Shelf Airborne Electronic Hardware Assurance Methods— Phase 3—Commodity Memories

June 2017

Final Report

This document is available to the U.S. public through the National Technical Information Services (NTIS), Springfield, Virginia 22161.

This document is also available from the Federal Aviation Administration William J. Hughes Technical Center at actlibrary.tc.faa.gov.

U.S. Department of Transportation Federal Aviation Administration

#### NOTICE

This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The U.S. Government assumes no liability for the contents or use thereof. The U.S. Government does not endorse products or manufacturers. Trade or manufacturers' names appear herein solely because they are considered essential to the objective of this report. The findings and conclusions in this report are those of the author(s) and do not necessarily represent the views of the funding agency. This document does not constitute FAA policy. Consult the FAA sponsoring organization listed on the Technical Documentation page as to its use.

This report is available at the FAA William J. Hughes Technical Center's Full-Text Technical Reports page: actlibrary.tc.faa.gov in Adobe Acrobat portable document format (PDF).

**Technical Report Documentation Page**

| 1. Report No.                                             | Government Accession No.           | Recipient's Catalog No.               |

|-----------------------------------------------------------|------------------------------------|---------------------------------------|

| DOT/FAA/TC-16/40                                          |                                    |                                       |

| 4. Title and Subtitle                                     |                                    | 5. Report Date                        |

| COMMERCIAL OFF-THE-SHELF AI<br>ASSURANCE METHODS—PHASE 3— | June 2017                          |                                       |

| MEMORIES                                                  | 6. Performing Organization Code    |                                       |

| 7. Author(s)                                              |                                    | Performing Organization Report No.    |

| Laurence H. Mutuel, Vincent Brindejonc,                   | D8                                 |                                       |

| Performing Organization Name and Address                  | 10. Work Unit No. (TRAIS)          |                                       |

| Thales Avionics, Inc.                                     |                                    |                                       |

| 2733 South Crystal Drive, Suite 1200                      | 11. Contract or Grant No.          |                                       |

| Arlington, VA 22202                                       |                                    |                                       |

| 12. Sponsoring Agency Name and Address                    |                                    | 13. Type of Report and Period Covered |

| Federal Aviation Administration                           | Final Report                       |                                       |

| FAA National Headquarters                                 |                                    |                                       |

| 950 L'Enfant Plaza SW                                     | November 2014 to November 2015     |                                       |

| Washington, DC 20024                                      | 14. Sponsoring Agency Code AIR-134 |                                       |

15. Supplementary Notes

The FAA William J. Hughes Technical Center Aviation Research Division Technical Monitors were Chakradhar Agava and Charles W. Kilgore, II (retired).

16. Abstract

This report deals with the issue of using commodity memories in avionics, explains the reasons for the concern, and investigates methods used to ensure the reliability of the data stored in commodity memories. Because of the competitive nature regarding the efforts by manufacturers to produce devices that have vast numbers (i.e., millions and possibly billions) of these memories, their quality can be suspect, and their reliability and availability are likely to be less robust. Four types of commodity memories are covered in this report: double data rate, not-AND flash, toggle magnetoresistive, and quad data rate. This report provides a brief description of the technologies, manufacturing aspects, and defect management of these memories. Confidence in commodity memories is built not only from matching their type to the domain usage in the design phase but also by actively engaging with the commodity manufacturer and distributor.

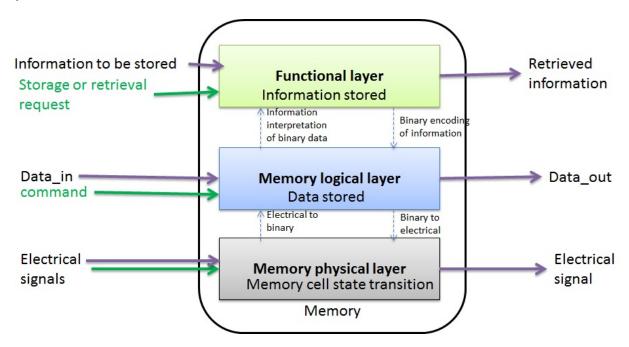

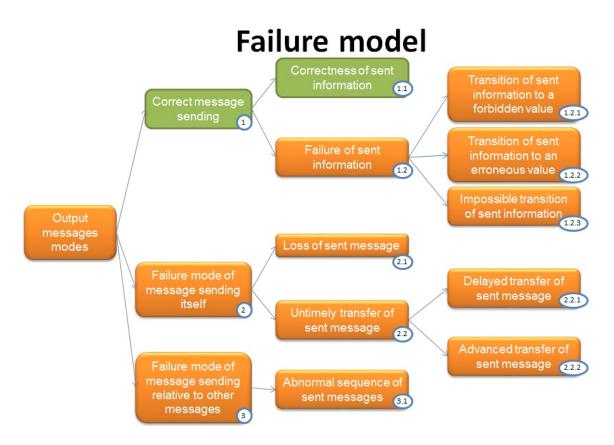

For the selected commodity memories, failure modes and failure mechanisms are discussed to illustrate the concern. Failure modes in commodity memories are described by using both a black-box and a grey-box model view and applying three levels of abstraction: functional, logical, and physical.

Ensuring the reliability of these commodity memories is investigated through the existing fault mitigation techniques embedded in these memories and the identification of additional internal or external fault mitigation techniques. Error correcting codes are the typical built-in mitigation technique for each of the selected commodity memory types. Issues with built-in mitigation techniques typically point to a lack of documentation or poor coverage of the Airborne Electronic Hardware usage domain.

Finally, the report presents a series of recommendations to support assurance of commodity memories in avionics products.

17. Key Words

Commercial off-the-shelf, Commodity memory, Double data rate, Quad data rate, Magnetoresistive random access memory, Static random access memory, Not-AND flash memories, Supply chain, Failure mode, Error correcting code, Error detection and correction, Airborne electronic hardware,

18. Distribution Statement

This document is available to the U.S. public through the National Technical Information Service (NTIS), Springfield, Virginia 22161. This document is also available from the Federal Aviation Administration William J. Hughes Technical Center at actlibrary.tc.faa.gov.

| 19. Security Classif. (of this report) | 20. Security Classif. (of this page) | 21. No. of Pages | 22. Price |

|----------------------------------------|--------------------------------------|------------------|-----------|

| Unclassified                           | Unclassified                         | 115              |           |

Redundancy, Memory test

# ACKNOWLEDGEMENTS

The research that led to this report was coordinated with the technical experts and reviewers at Thales Avionics SAS by Cyril Marchand. Didier Regis and Guy Berthon acted as internal reviewers for this report.

# TABLE OF CONTENTS

|      |            |                                  |                                                                                                                                                                    | Page                 |

|------|------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| EXEC | CUTIVE     | E SUMN                           | MARY                                                                                                                                                               | X                    |

| 1.   | INTR       | ODUCT                            | ΓΙΟΝ                                                                                                                                                               | 1                    |

|      | 1.1<br>1.2 | Backg<br>Purpos                  |                                                                                                                                                                    | 1 2                  |

| 2.   | IDEN       | TIFICA                           | TION OF COMMODITY MEMORIES FOR AEH PURPOSES                                                                                                                        | 2                    |

|      | 2.1<br>2.2 |                                  | em statement<br>ed Types of Commodity Memories                                                                                                                     | 2 3                  |

|      |            | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4 | Double Data Rate Synchronous Dynamic Random Access Memories<br>Not-AND Flash Memories<br>Quad Data Rate Memories<br>Toggle Magnetoresistive Random Access Memories | 3<br>5<br>9<br>11    |

|      | 2.3        | Supply                           | y Chain Considerations                                                                                                                                             | 13                   |

|      |            | 2.3.1<br>2.3.2<br>2.3.3          | Memory Manufacturers Distributors Summary                                                                                                                          | 14<br>18<br>19       |

|      | 2.4        | Usage                            | Domain                                                                                                                                                             | 19                   |

| 3.   | FAIL       | URE M                            | ODES AND FAILURE MECHANISMS                                                                                                                                        | 20                   |

|      | 3.1        | Descri                           | iption of failure mode Types in Commodity Memories                                                                                                                 | 20                   |

|      |            | 3.1.1<br>3.1.2                   | Issues With Commodity Memories Failure Mode Analysis<br>Detailed Analysis of the Selected Memory Families                                                          | 20<br>25             |

|      | 3.2        | Failur                           | e Mechanisms for Commodity memories                                                                                                                                | 33                   |

|      |            | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4 | Introduction Die Failures Package-Related Failures Synthesis Tables of Die Defects and Defects Induced by Packaging                                                | 33<br>34<br>40<br>43 |

| 4.   | MITIO      | GATIO                            | N OF FAILURE MODES                                                                                                                                                 | 46                   |

|      | 4.1        | Embed                            | dded Mitigations                                                                                                                                                   | 46                   |

|      |            | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                   | Embedded Mitigation in DDR Memories Embedded Mitigation in NAND Flash Memories Embedded Mitigation in QDR Memories Embedded Mitigation in Toggle Magnetoresistive RAM                                                                                                                                                         | 48<br>48<br>49<br>49       |

|------|------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|      | 4.2<br>4.3 |                                                    | ial Issues with Embedded Mitigation Techniques veness of EDC Mitigation Technique                                                                                                                                                                                                                                             | 49<br>50                   |

|      |            | 4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                   | Overview of EDC Technique Effectiveness of an ECC Mechanism Methods for Analyzing the Effectiveness of a Real ECC Mechanism Application to the Selected Commodity Memories                                                                                                                                                    | 50<br>51<br>54<br>55       |

|      | 4.4        | Interna                                            | al or External Fault Mitigation Techniques Other than Built-in Solutions                                                                                                                                                                                                                                                      | 56                         |

|      |            | 4.4.1<br>4.4.2<br>4.4.3<br>4.4.4                   | Reducing the Probability of Occurrence of Data Alteration<br>EDC<br>Mixing Redundancy and EDC<br>Summary of Fault Mitigation Techniques With Respect to Identified<br>Memory Fault Types                                                                                                                                      | 56<br>69<br>82<br>82       |

|      | 4.5        | Identif                                            | ication of Needed Improved EDC Mitigation Techniques                                                                                                                                                                                                                                                                          | 83                         |

|      |            | 4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.5.5<br>4.5.6 | Classification of Information According to Criticality Improved Mitigation Techniques for DDR Memories Improved Mitigation Techniques for NAND Flash Memories Improved Mitigation Techniques for QDR Memory Improved Mitigation Techniques for MRAM Summary of Improved Mitigation Techniques for Selected Commodity Memories | 83<br>84<br>85<br>86<br>87 |

| 5.   | RECO       | MMEN                                               | DATIONS AND FINDINGS                                                                                                                                                                                                                                                                                                          | 88                         |

|      | 5.1<br>5.2 |                                                    | ary of Findings<br>nmendations                                                                                                                                                                                                                                                                                                | 88<br>89                   |

|      |            | 5.2.1<br>5.2.2<br>5.2.3                            | Supply Chain Selection and Control<br>Careful Definition of Domain Usage<br>Management of Manufacturing Defects                                                                                                                                                                                                               | 89<br>90<br>90             |

| 6.   | REFE       | RENCE                                              | S                                                                                                                                                                                                                                                                                                                             | 92                         |

| APPE | NDICES     | S                                                  |                                                                                                                                                                                                                                                                                                                               |                            |

|      | A—GI       | LOSSA                                              | RY                                                                                                                                                                                                                                                                                                                            |                            |

B—NAND AND NOR FLASH MEMORIES

C—EXAMPLE OF QUALITATIVE MEMORY FMEA

# LIST OF FIGURES

| Figure |                                                                                 | Page |

|--------|---------------------------------------------------------------------------------|------|

| 1      | Composition of the supply chain for this report                                 | 13   |

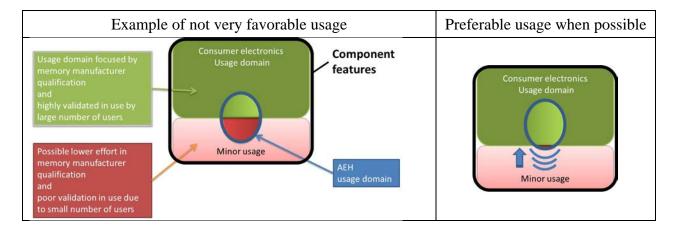

| 2      | Comparison of favorable and not-favorable usage domains                         | 20   |

| 3      | Three-layer model of a memory                                                   | 21   |

| 4      | Tree of possible failure modes                                                  | 23   |

| 5      | Simplified DDR memory block diagram                                             | 26   |

| 6      | Simplified NAND flash memory block diagram                                      | 28   |

| 7      | Simplified QDR memory block diagram                                             | 30   |

| 8      | Simplified toggle MRAM block diagram                                            | 32   |

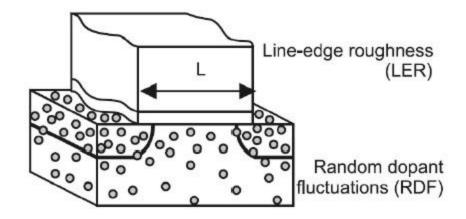

| 9      | Primary sources of process variation: RDF and LER 0                             | 35   |

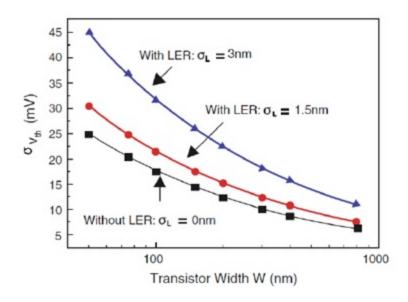

| 10     | Combined effect of LER on $V_{th}$ variation                                    | 36   |

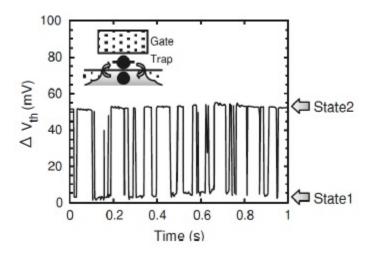

| 11     | RTN $V_{th}$ variation caused by trapping and detrapping charges in the channel | 36   |

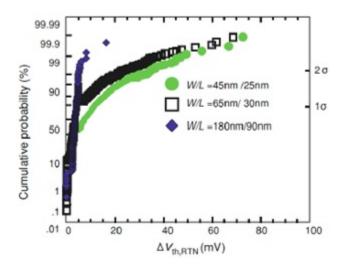

| 12     | Distribution of $V_{th}$ fluctuation due to RTN                                 | 37   |

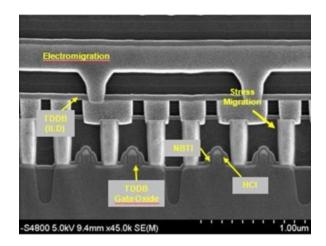

| 13     | Wear-out phenomena localization (65 nm IC cross section)                        | 39   |

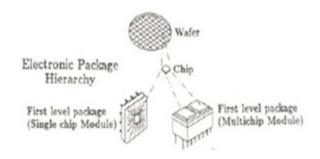

| 14     | First level package 29                                                          | 40   |

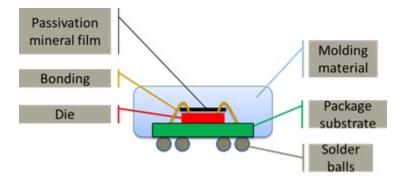

| 15     | View of a package                                                               | 41   |

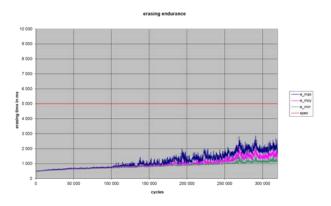

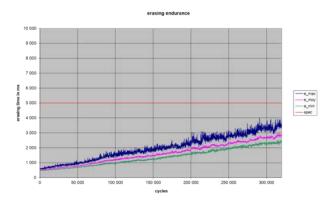

| 16     | Erasing endurance for original NOR flash memory                                 | 57   |

| 17     | Erasing endurance for the same reference with simple technology shrink option   | 58   |

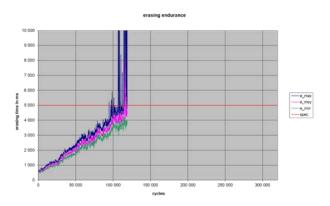

| 18     | Erasing endurance for the new die design option                                 | 58   |

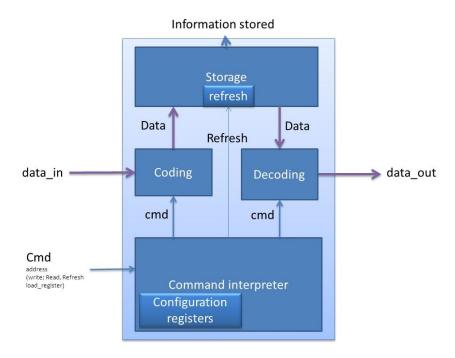

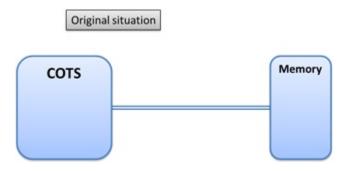

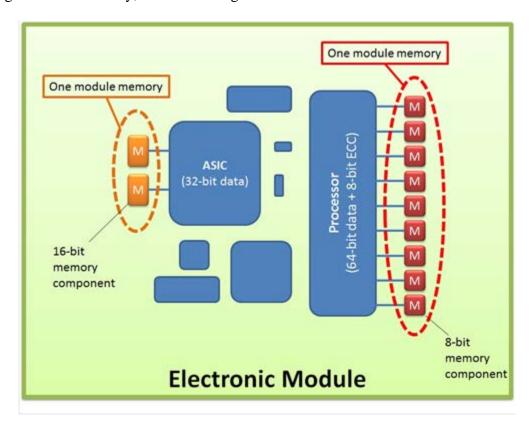

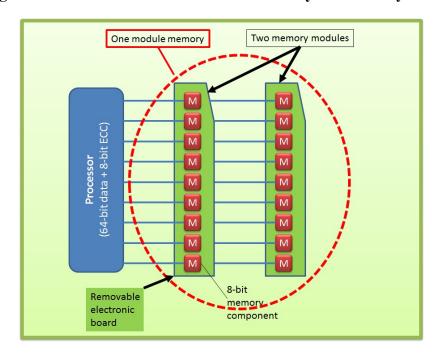

| 19     | Original configuration of a COTS and module memory                              | 72   |

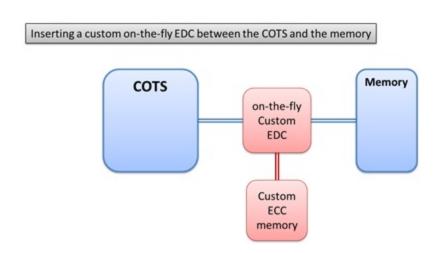

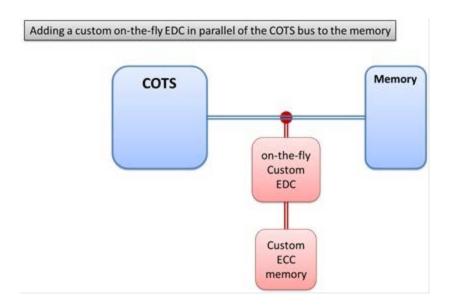

| 20     | Custom on-the-fly EDC inserted between the COTS and module memory               | 73   |

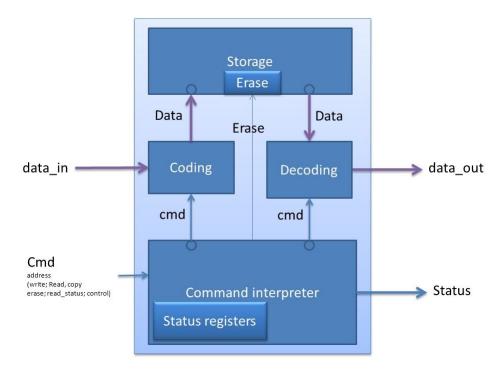

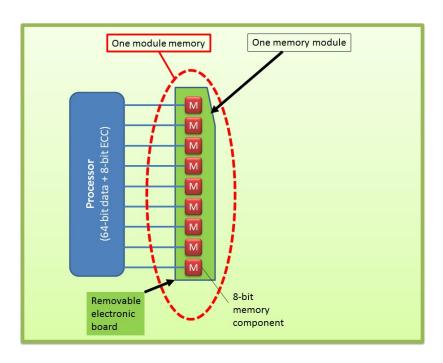

| 21     | Custom on-the-fly EDC inserted on the bus between the COTS and module memory    | 74   |

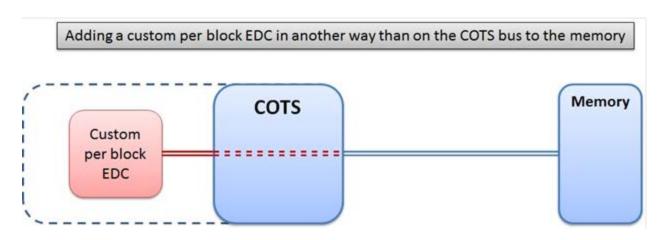

| 22     | Custom per block EDC inserted on the internal bus of the COTS component         | 75   |

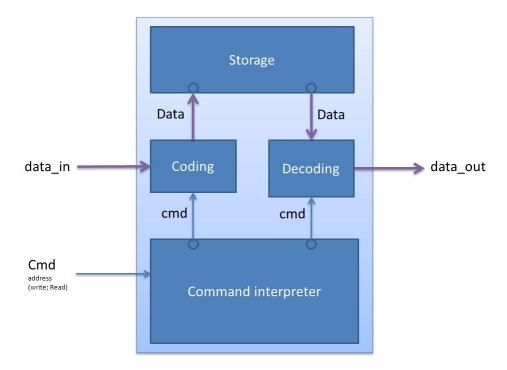

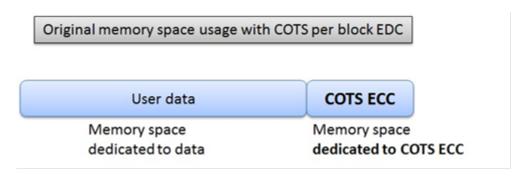

| 23     | Original configuration of a memory with COTS per block EDC                      | 75   |

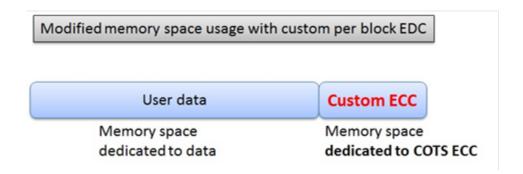

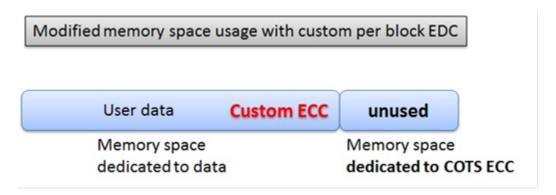

| 24     | Custom per block ECC replacing COTS ECC                                         | 76   |

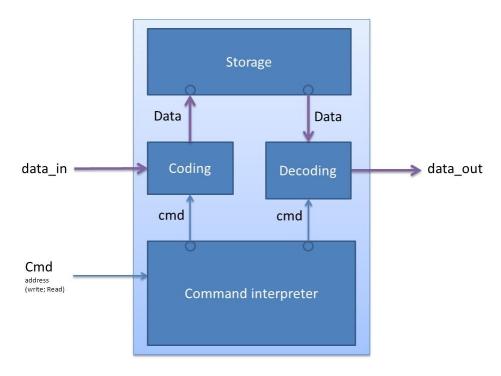

| 25     | Custom per block ECC added as extra data                                        | 76   |

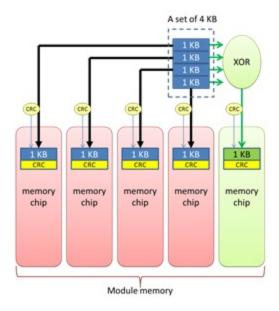

| 26     | Example of RAID5 principle applied to commodity memory                          | 81   |

# LIST OF TABLES

| Table |                                                                       | Page |

|-------|-----------------------------------------------------------------------|------|

| 1     | List of commodity memories selected for the research                  | 3    |

| 2     | Summary of available documentation                                    | 18   |

| 3     | Relationship between package constituents and package functions       | 42   |

| 4     | Synthesis of die defects                                              | 44   |

| 5     | Synthesis of memory defects induced by packaging                      | 45   |

| 6     | Summary of mitigation per memory type                                 | 47   |

| 7     | Example of ECC status table                                           | 52   |

| 8     | Main advantages and drawbacks of redundancy options                   | 64   |

| 9     | Example implementation of redundancy using existing memory components | 66   |

| 10    | Example use of redundancy using existing memory components            | 66   |

| 11    | Summary of mitigation techniques versus fault types                   | 83   |

| 12    | Summary of improved mitigation per memory type                        | 88   |

| 13    | Template for recommendations                                          | 89   |

#### LIST OF ABBREVATIONS AND ACRONYMS

AEH Airborne electronic hardware AFE Authority for Expenditure

ASIC Application-specific integrated circuit BCH Bose-Chaudhuri-Hocquenghem

BGA Ball grid array

BTI Bias temperature instability CFR Code of Federal Regulations

CMOS Complementary metal-oxide semiconductor

COTS Commercial-off-the-shelf CRC Cyclic redundancy code

DDR Double data rate

DRAM Dynamic random access memory

ECC Error correcting code

EDC Error detection and correction

EEPROM Electrically erasable programmable read only memory

EM Electro-migration

FMEA Failure modes and effects analysis FPGA Field programmable gate array

HCI Hot carrier injection IC Integrated circuit

ISO International Organization for Standardization JEDEC Joint Electron Device Engineering Council

LER Line-edge roughness MLC Multi-level cell

MOS Metal-oxide semiconductor

MRAM Magnetoresistive random access memory

NAND Not-AND

NDA Non-disclosure agreement

NOK Not Okay NOR Not-OR

NVSRAM Non-volatile static random access memory

OK Okay

PCB Printed circuit board PLD Programmable logic device

PROM Programmable read-only memory

QDR Quad data rate

RAID Redundant arrays of independent drives

RAM Random access memory

RDF Random dopant fluctuation

RTN Random telegraph noise

RTS Random telegraph signal

SDRAM Synchronous dynamic random access memory

SDS Software and Digital Systems

SECDED Single error correction, double error detection

SEU Single event upset

SIV Stress-induced voiding

SLC Single-level cell

Static random access memory **SRAM**

Spin transfer torque STT

TCE

Thermal coefficient expansion

Time-dependent dielectric breakdown TDDB

TLC Triple-level cell Threshold voltage  $V_{th}$ WSE Write soft error **XOR** Exclusive logical OR

#### **EXECUTIVE SUMMARY**

This report deals with the main issues of using commodity memories in avionics, including safety-critical products. Because of the competitive nature of manufacturers to produce devices that have vast numbers (i.e., millions and possibly billions) of these memories, their quality can be suspect and their reliability and availability are likely to be less robust. This report explains the reason for the concern and investigates methods employed to ensure the reliability of the data stored in commodity memories. Four types of commodity memories are covered in this report to illustrate the nature of the issue. Double data rate memories and Not-AND flash memories are currently being used in avionics products, whereas toggle magnetoresistive memories and quad data rate memories are foreseen to be widely used by aerospace equipment manufacturers in the near future. This report provides a brief description of the technologies, manufacturing aspects, and the state-of-the-art defect management that is used during the manufacture of these technologies.

Confidence in commodity memories is built not only from matching their type to the domain usage in the design phase but also by actively engaging with two key entities in the supply chain: the commodity manufacturer and the distributor. This engagement is required to access necessary supporting documentation and understand internal workings not otherwise accessible. A non-disclosure agreement is required, although it might not be sufficient on its own.

Failure modes and failure mechanisms for the selected commodity memories are discussed to illustrate the concern. Failure modes in commodity memories are described by using both a black-box and grey-box model view and applying three levels of abstraction: functional, logical, and physical. This organization of information allows for the description of generic functional failure modes associated with writing, preserving, and reading data in a memory; description of failure modes associated with data flows; and refinement of failure mode analysis using physical characteristics. For each of the selected types of commodity memories, this report provides specific examples of functional failure modes applied to each of the data flows. Failures associated with the die and packaging are presented in this report. For each defect type, the impacted memory components, as well as the type of error (soft or hard) and the potential systematic impact at production batch level, are identified.

Ensuring the reliability of these commodity memories is investigated through the existing fault mitigation techniques (e.g., Error Correcting Codes [ECCs]) embedded in these memories and the identification of additional internal or external fault mitigation techniques. ECC represent the typical built-in mitigation technique for each of the selected commodity memory types. The mitigation may be implemented by the manufacturer, user, or both. Little or no information is publicly available regarding the embedded ECC for three of the covered types of memory, reinforcing the earlier finding that the airborne electronic hardware (AEH) manufacturer should interact with the memory manufacturer to not only understand the existence of mitigation but the possible configurations and limitations as well. Issues with built-in mitigation techniques typically point to a lack of documentation or poor coverage of the AEH usage domain. Analyzing the effectiveness of the built-in mitigation techniques should be done with respect to the number of errors and type of triggering events the mitigation can handle. The analysis must cover all elements of the embedded mitigation. The approach can be theoretical or experimental, but in both cases sufficient information can be obtained only via the memory manufacturer.

After the use of memory tests to reduce the likelihood of occurrences of data alteration, additional mitigation can be obtained through the use of external means, such as redundancy, or by enhancing the error detection and correction capability of the memory (or a combination of both). For each of the selected commodity memories, the report provides recommendations detailing the applicability of each technique.

Finally, the report presents a series of recommendations to support the safety assurance of commodity memories in avionics products. The recommendations are organized by the supply chain selection and control, definition of usage domain, and management of manufacturing defects for each type of selected commodity memory.

#### 1. INTRODUCTION

#### 1.1 BACKGROUND

Commercial-off-the-shelf (COTS) items are increasingly penetrating into both the commercial and the military segments of the aerospace market. RTCA standards, namely DO-254 "Design Assurance Guidance for Airborne Electronic Hardware" [1] and DO-178C "Software Considerations in Airborne Systems and Equipment Certification" [2], were developed with the issue of COTS assurance in mind. However, these standards do not recommend specific methods or objective criteria for COTS safety assurance and airworthiness.

In a general context of airworthiness, the focus of this report is threefold:

- Intended function (Title 14 Code of Federal Regulations Part [14 CFR] 2x.1301): component selection from a functional standpoint and design to meet the function contributing to this aspect.

- Operating conditions (14 CFR 2x.1309): component selection from the point of view of characteristics and performance and environmental qualification of these components contribute to this aspect.

- Safe operation (14 CFR 2x.1309): failure modes and failure mitigation of the selected components contribute to this aspect. Reliability considerations are integrated into the demonstration of achievement of safe operation.

The research thrust on COTS Airborne Electronic Hardware (AEH) assurance methods addresses "safe operation" and supports the development of a comprehensive framework for COTS safety assurance. The framework includes:

- The understanding of current and foreseen future use of COTS in AEH.

- The description of safety issues and concerns.

- The documentation of failure modes for these COTS and the relevance to AEH context.

- The investigation of existing mitigation techniques and their effectiveness.

- The development of objective criteria for determining the effectiveness of safety and airworthiness assurance methods for AEH integrating the COTS under consideration.

Previous research under Authority for Expenditure (AFE) project 75 (COTS AEH Assurance Methods) documented 22 COTS issues and proposed a structure to address future COTS AEH assurance standards [3]. A continuation of the research on the identified issues with COTS is currently allocated in part to a supplement to AFE project 75 phase 3 research task order under the Software and Digital Systems (SDS) program, whose focus is commodity memories and embedded microcontrollers [4].

This report is produced under the SDS program. It refines the more general COTS AEH assurance methods for the use of commodity memories. In the process of describing the COTS commodity memories in AEH, considerations of intended function and operating conditions are integrated into the discussion.

#### 1.2 PURPOSE

This report deals with the main issues of using commodity memories in avionics, including safety-critical products. Because of the competitive nature of the efforts by manufacturers in producing devices that have vast numbers (i.e., millions and possibly billions) of these memories, their quality can be suspect and their reliability and availability are likely to be less robust. The report explains the reason for the concern and investigates methods to ensure the reliability of the data stored in commodity memories.

Several types of commodity memories are covered in this report to fully illustrate the nature of the issue. They are currently being used or might be used in the near future by aerospace equipment manufacturers. For the selected commodity memories, failure modes and failure modeling are being discussed to illustrate the concern. Assuring the reliability of these commodity memories is investigated through the existing fault mitigation techniques (e.g., Error Correcting Codes [ECCs]) embedded in these memories and the identification of additional internal or external fault-mitigation techniques. Finally, the report presents a series of recommendations to support the assurance of commodity memories in avionics products.

## Disclaimer:

In this report, we may state that some COTS components in which the primary target is the consumer electronics market exhibit a level of quality that does not meet AEH quality requirements, especially for safety-critical applications. This statement does not mean in any way that the manufacturers may be lax or incompetent. What is meant is that manufacturing and supply processes that are perfectly rigorous and appropriate for the consumer electronics market may not meet AEH requirements.

#### 2. IDENTIFICATION OF COMMODITY MEMORIES FOR AEH PURPOSES

This section contains introductory material, including descriptions of various types of commodity memories that are being used and might be used in the near future by aerospace equipment manufacturers. The description is set in a context for which the initial market of these memories is not the aerospace market, which has a direct consequence on the type of issues that can be encountered with these products (i.e., because the non-aerospace market controls this initial market, the aerospace industry does not have a great influence on the issues that will be mainly handled by that other industry).

#### 2.1 PROBLEM STATEMENT

By definition, a commodity is a mass-produced, unspecialized product. The main market for commodity memories is consumer electronics, whose characteristics include:

- A very large production volume.

- A very high level of competition.

- Pressure to achieve the shortest possible time to market.

- A fast technology refresh cycle (i.e., short time lapse to the next generation).

- A short market lifetime of consumer devices embedding memories.

As a consequence of the last two bulleted items above, the continuity of support for a given generation of commodity memory is limited.

The level of quality of memories, although meeting relevant safety standards and regulations (e.g., ISO-2859-1 [5]), is mainly driven by trading considerations. In consumer electronics, the failure of a memory is likely to impact the end-users' satisfaction level rather than their safety.

This market context is quite different from the avionics market, for which safety is a major driving force. From consumer electronics market characteristics, AEH manufacturers could fear that the intrinsic competitive pressure may eventually result in a slightly lowered quality of the commodity production. This lower quality would still be fully compatible with consumer electronics safety standards, but it may not be adequate for avionics safety requirements. Therefore, the question is not whether commodity memories are of good quality but whether commodity memories have the level of quality adequate for AEH.

# 2.2 SELECTED TYPES OF COMMODITY MEMORIES

This section describes commodity memories selected for their current widespread use and their foreseen widespread use. The objective of this section is to provide a purposely short and simplified technical description sufficient to promote the understanding of the issues associated with the use of commodity memories in AEH and the subsequent discussion on failure mode and failure mitigation. Table 1 lists the commodity memories selected for this investigation along with their usage level from a market standpoint.

Table 1. List of commodity memories selected for the research

| Memory Type | Usage Level and Market                            |

|-------------|---------------------------------------------------|

| DDR SDRAM   | Widely used in consumer electronics market        |

| QDR RAM     | Mainly used in industrial applications            |

| NAND FLASH  | Widely used in consumer electronics market        |

| MRAM        | Not yet widely used but may be in the near future |

DDR = double data rate; SDRAM = synchronous dynamic random access memories

QDR = quad data rate; NAND = not-AND; MRAM = magnetoresistive random access memory

# 2.2.1 Double Data Rate Synchronous Dynamic Random Access Memories

Double data rate (DDR) synchronous dynamic random access memory (SDRAM) is present in force in consumer electronics devices. It represents a massive and very competitive market with a high production volume and growth rate.

DDR SDRAMs are widely used in AEH as the main memory of almost all processors. They are also often associated with programmable logic devices (PLDs) and application-specific integrated circuits (ASICs) for building large memory areas that would not otherwise fit inside the PLD or ASIC. The wide use of DDR memories stems from their combining large capacity and high performance with relatively low cost. Because DDR memories are a critical type of memory for AEH, they require attention by the aerospace industry.

#### 2.2.1.1 Technical Overview

DDR memories are dynamic random access memories (DRAM): the storage element is made of a small capacitor that holds a binary datum (zero or one) corresponding to either a charged or discharged state. This technology enables the memory cells to be smaller than if they were implemented with only transistors. A smaller size allows for higher density, which is the primary reason for the popularity of DRAM.

The DDR denomination simply refers to the data bus flow. The data bus transfers one datum on both the rising edge and the falling edge of the clock or two data in a single-clock period. The double rate only pertains to data and only at the external bus interface level. The rest of the die works at the clock rate, including internal data buses. To match the DDR, the internal data bus is simply twice as wide as the external data bus.

Successive generations of DDR memories are designated as DDR1, DDR2, DDR3, DDR4, and so on. The difference between the successive generations mainly refers to the operating frequency, as the component architecture and internal operation do not change significantly. The clock frequency is regularly increased to improve data flow performance. The increases primarily affect the interfaces while keeping the increase in intrinsic speed of the memory cell to a minimum. The external growth of the data rate is obtained by simultaneously accessing a greater number of memory cells. For example, consider a memory array working internally at 100 MHz: reading simultaneously 32 internal bits supports 8 bits at 400 MHz on the external bus, while reading simultaneously 64 internal bits supports 8 bits at 800 MHz on the external bus. Raising the clock frequency requires not only improvement on the silicon technology but also on the low-level electrical interface between the memory chip and the board. Examples of such improvements on the electrical interface include lower voltage range, automatic skew compensation, and line-termination management. Changing the electrical interface has nonnegligible consequences: successive generations of DDR memories are incompatible.

# 2.2.1.2 Manufacturing Aspects

As the memory capacity grows, the scale of the transistors and capacitors is reduced, as is the supply voltage. Producing capacitors that have both a small surface on the die and a capacitance that remains high enough to store a significant amount of electrical charge under a lower voltage is rather difficult. Each manufacturer has its own—and generally confidential—method for solving this problem. Sample solutions include implementing capacitors with vertical shafts (the surface of the capacitor being the surface of a cylinder) that take advantage of the third dimension to increase the area of the capacitor while maintaining a small footprint on the die. Furthermore, special materials can cause the surface of the shaft to be granular, which increases the useful area. Finally, internal charge pump mechanisms may be implemented to feed the capacitor with higher voltages than the chip's supply voltage.

Regardless of the realization, the solutions described above increase the risk of producing bad memory cells during the manufacturing process. On the other hand, rejecting a die for the sole reason that a single capacitor is defective would have a severe impact on the production yield. The following technique may be implemented to prevent the rejection of die with only a few defective cells: the memory design can include rows of cells additional to the number of rows

necessary to achieve the memory size as pointed out by the data sheet. During manufacturing tests, rows with defective cells are identified, and an internal mechanism reroutes the address of each defective row to a (good) spare row (e.g., by using thermal or laser fuses). This mechanism is kept confidential. Publicly available documents describe this method in general terms, but there is no mention of it in the available documentation from the manufacturers. It is mentioned in this report only as a likely implementation.

A "good" DDR die is not necessarily a die without defects; rather, a die may possess defects for which a work around has been developed or for which compensation has been applied.

#### 2.2.1.3 Management of Manufacturing Defects

Naturally occurring manufacturing defects are normally managed during the production process either by employing a workaround or by rejecting the dies that cannot be fixed. However, full testing of all memory cells of the die is more expensive than sampling tests or parametric tests. Therefore, one of the concerns is related to the potential risk that the amount of testing will be reduced to minimize the production testing costs. Even if testing is expensive, delivering components with poor quality certainly has a higher cost; indeed, in consumer electronics devices, a DDR memory is a critical component. A defect in a DDR memory chip generally prevents the equipment from working correctly. Moreover, since almost all systems perform a memory test at startup, a faulty DDR memory chip soldered on an electronic board would quickly be detected by the customer, who in turn would be unsatisfied. Therefore, it is unlikely that manufacturers intentionally deliver defective DDR memory chips to customers, who buy them in the tens of millions.

However, defects may exist that are unlikely to be visible in consumer electronics devices but more likely to be visible in an industrial or avionics application. For example, consider the problem of bits flipped by intensive reading of the same row of a DDR memory. In common usage, in which a DDR memory is mainly accessed by software, such particular access sequences do not occur. However, in a specific application, such as a DDR memory connected to an ASIC, the repeated access sequence might occur in special cases. For memories intended to be used in consumer electronics applications, adding a production test dedicated to this issue might not be worthwhile. However, for memories intended to be used in industrial or avionics equipment of assurance level A, a full test is desirable because the correct behavior must be guaranteed for all access sequences. In general, the level of testing must be commensurate with the safety level required for operation of that device (e.g., along the lines of a system development assurance level, as shown in the DO-254 guideline document).

The production tests and qualification process of the DDR memory chips are important factors for selecting a DDR memory for AEH. Consideration of the supply chain to support this selection is further discussed in section 2.3.

#### 2.2.2 Not-AND Flash Memories

Not-AND (NAND) flash memories are present in most consumer electronic devices. They represent a highly competitive massive market with a significant volume production and growth rate. NAND flash memory technology evolves very rapidly.

NAND flash memories are used in AEH, where mass memory is needed, for example, in cockpit display equipment to store images of maps, in-flight management systems (FMS) to store navigation databases, and integrated modular avionics to store varied large databases for the hosted applications. NAND flash memories are popular because of their advantageously combining significant capacity with high integration and low cost.

Because of wear, NAND flash memories require specific management in their use. For this reason, they are generally associated with a dedicated microcontroller that offers two services:

- A standard interface to the main processor or PLD/ASIC that uses the mass memory independent of the evolution of the interface of the NAND flash memory chips themselves. This is particularly useful because NAND flash memory chip interfaces evolve quickly to incorporate more improvements to fit with the continuous increases in size and speed of the components. Examples of such standard interfaces are integrated drive electronics and serial advanced technology attachment interfaces.

- The management of all tasks induced by the wear of the component. The evolutions of the wear management are embedded inside the microcontroller and do not impact the rest of the equipment. This is particularly valuable because NAND flash memory chips evolve quickly and wear management must evolve accordingly.

The microcontroller can be separately purchased from the NAND flash memory chips and assembled on the board. Some manufacturers propose integrated solutions in which the microcontroller and NAND flash memory chips are integrated in a single chip (called a compound chip). One must keep in mind that integrated mass memory devices contain NAND flash memory chips. In this case, it is more difficult to have access to information about the actual embedded NAND flash memory chips, so particular attention must be paid to this point when selecting devices. Microcontrollers are not within the scope of the present document, so, therefore, only the NAND flash memory chips themselves will be addressed.

#### 2.2.2.1 Technical Overview

NAND flash memories are flash programmable read-only memory (PROM). Non-volatile memorization is obtained by trapping electrons in a dedicated area near the gate of a metal-oxide semiconductor (MOS) transistor, which changes its characteristics (general principle). Programming and erasing consist of injecting or extracting electrons to or from the electron trap.

Reading consists of driving the transistor and measuring the voltage at its output with an analog comparator. Depending on whether or not there are electrons in the trap, the voltage will be different. Injecting or extracting electrons to or from the electron trap requires voltage greater than the chip's power supply. To generate these higher voltages, the chip contains charge pump mechanisms.

Two main variants of NAND flash memory exist: single-level cell (SLC) and multi-level cell (MLC). The SLC variant works in a hybrid manner: the voltage at the output of the transistor can take only two values driven by the presence, or lack of presence, of electrons in the trap. Thus, a single transistor can store one bit of information. The MLC variant works within a multivaried

atmosphere. There may be four different amounts of electrons in the trap: empty, one-third full, two-thirds full, or full. The voltage at the output of the transistor can therefore take four different values, and a single transistor can store two bits of information. Another variant exists that uses eight levels, so that a transistor can store three bits of information. It is often referred to as triple-level cell (TLC). This third variant is less frequently used than the two main variants described above because the TLC has significantly lower erase and write endurance.

The advantage of the MLC variant, which makes it very popular, is that it provides twice the capacity for the same die area. The drawback of the MLC is that it requires much stricter control of the amount of electrons in the trap. The main consequence is that the MLC wears faster than the SLC. One of the causes of wear is that during programming of erasing, some electrons get caught near the trap and can no longer be removed. These stuck electrons create a bias on the voltage at the output of the transistor. A lower number of stuck electrons is necessary to create a false voltage on a four-level cell than on a two-level cell, and that critical number will therefore appear earlier for an MLC than for an SLC. Also, for similar reasons, the MLC is more sensitive to manufacturing defects than the SLC.

An intermediate variant called "pseudo SLC" is proposed by some manufacturers. A pseudo SLC is a die that has been designed for MLC, so that each cell is able to take on four values but is internally underused: only the values "00" (empty) and "11" (full) are used among the four possible values of "00," "01," "10," and "11." This strategy allows the manufacturer to offer a chip with the same reliability as an SLC device while still using the same die manufacturing chain used for its MLC, allowing the company to save money. Nevertheless, one could imagine that on a given production line, the dies that are sold as pseudo SLC could be those MLC dies that failed the production test as 2-bit per cell but passed the test as 1-bit per cell. It could be a means for the manufacturer to cut their losses by selling these dies as half capacity-chips rather than rejecting them. This is conjecture, of course, but a safety approach must consider all cases; auditing the manufacturer is a key point.

Finally, a new generation of NAND flash memory is emerging as a three-dimensional variant. In this variant, several layers of cells are stacked one on top of the other on the same die. This is different from having several dies stacked one on top of the other. The three-dimensional variant consists of a single die built in a one-shot process. This technology is too recent to have accumulated enough service experience, so it is not taken into account in this report.

Two main sources produce defects in a NAND flash memory: manufacturing and wear. Wear occurs during erase, read, and program operations. There are two types of wearing effects:

- A temporary effect: some bits will "dim," possibly up to the loss of their information, but only the stored information is affected. The memory cell is intact and will work correctly at the next erase or program operation.

- A permanent effect: some internal elements break and can no longer be used. These elements may be individual cells (or sets of cells) or elements common to several cells, such as an erasing mechanism (charge pump for instance).

Normally, reading only causes data dimming, which may result in data loss but not in permanent damage.

# 2.2.2.2 Manufacturing Aspects

NAND flash memories have a very high density and embed a very large number of cells. It is expected that some cells are defective at the end of the die-manufacturing process. Because of the very high volume and very competitive market, it is not desirable to reject a die simply because one or a few cells are defective. Therefore, dies shipped to customers actually contain defective cells. The component contains an internal table at a dedicated location in the memory array, which contains the list of the defective cells so that the users can manage them on their own.

The situation in which a new product is expected to contain defects may be seen as beneficial for AEH because the manufacturers must provide facilities to handle these internal defects. Conversely, the percentage of defective chips that may be acceptable for consumer electronics might not be acceptable for AEH.

# 2.2.2.3 Management of Manufacturing Defects

As previously explained, NAND flash memories have initial defects in addition to the defects that will appear during the component life. All components that manage NAND flash memories will always include mechanisms (hardware or software, or both) to manage these defects. In addition, built-in facility assists in the management of defects: extra bytes dedicated to storing ECC are provided on the memory chip. The management of the ECC (computation, verification, and data correction) must be undertaken by the user.

In addition, extra data bytes are provided on the die. Consider the following theoretical example for a 100 MB nominal capacity for which the die may actually host 110 MB of data cells. The user never uses more than 100 MB. During the life of the product, some datasets fail and become unusable. The user stops using the defective cells and begins to use some of the spare cells instead, thus maintaining a usable memory space of 100 MB. The memory chip must be replaced when the amount of working memory cells fall under the minimum required for the system to work correctly.

The detection of defective data blocks is made at three distinct times:

- Erase time: If the erase operation fails, the chip provides a status informing the user that the operation failed. The corresponding block should be considered defective.

- Program time: If the write operation fails, the chip provides a status informing the user that the operation failed. The corresponding block should be considered defective.

- Read time: When a set of data is read, the ECC must be verified by the user to check the integrity of the read data. If the ECC reports errors, the user may decide whether to carry on using this data block or declare it defective. The decision is user-defined and may rely for instance on the status of the ECC (e.g., number of altered bits) or on a counter that indicates how many times this block has reported ECC errors despite events, such as erasure or program cycles.

It is the responsibility of the user (consumer or AEH user) to maintain a list of the data blocks identified as defective. This list may itself be stored in the NAND flash memory, provided that enough care is taken, typically through redundancy. Management of the remapping of failed blocks versus spare blocks must be made by the user.

Placing the above information in the context of AEH requirements, the following should be considered:

- The ECC has a limited capacity in terms of number or erroneous bits that can be correctly detected. If there are too many faulty cells, the ECC will produce a false status. A concern should therefore arise when manufacturing quality unreported by testing leads to defective cells whose number exceeds the ECC capability.

- If the cells wear too quickly, the life duration of the component will be too short with respect to AEH requirement (including an end-of-life event in flight). The defects appearing during the life of the component are not detected by quality control at delivery. A concern should therefore arise when the manufacturing quality process does not, or does, limit wear-endurance testing.

These considerations tie to the selection of a reliable supply chain, as detailed in section 2.3.

# 2.2.3 Quad Data Rate Memories

Quad data rate (QDR) memories are a special type of static random access memory (SRAM). The QDR memory market is mainly an industrial one focused on the telecommunication domain for ground stations managing traffic routing. These memories seem to have been created specifically to address this purpose. Although the quality level required by telecommunication applications is not that of safety-critical applications, it is higher than that required for the consumer electronics market because a failure of one such ground-heavy station has greater financial impact than a failure of one personal device. From an AEH concerns point of view, QDR memories are less subject to risk than the types of memories previously discussed. Finally, QDR memories are generally not present in consumer electronics devices because of their higher price. Therefore, DDR memories are preferred in the consumer electronics market.

QDR memories are used in AEH but not as widely as the other types of memories because their cost is much higher than DDR memories. They are used when very high throughput is required and a relatively low capacity (i.e., a few megabytes) is acceptable. Whenever possible, DDR memories are preferred because they are cheaper. For cases in which DDR memories do not offer the necessary throughput, QDR memories are preferred despite the added cost and lower storage capacity.

QDR memories offer two advantages over DDR memories:

- A separate data-in and data-out bus, allowing simultaneous read and write operations at different addresses

- A low read latency—typically two clock periods instead of seven or more for the DDR memory—which allows much better performance for random accesses

QDR memories are mostly associated with PLD and ASIC because of their dedicated use and because their specific bus is generally not available on processors and microcontrollers. A typical application is network switch engines, for which frame management requires a high data exchange with buffer and configuration memories. Simultaneous read and write is an advantage because as much data need to be written to the buffers as to be read from them. Also, configuration memories (like routing tables) require random accesses and the low latency of the QDR memories is beneficial.

# 2.2.3.1 Technical Overview

The storage cell of a QDR memory is made only with complementary metal-oxide semiconductor (CMOS) transistors. Contrary to the other types of memories discussed in this report, there is no specific technology associated with QDR memories. What distinguishes them from other SRAM is their bus interface.

The bus interface is comprised of two separate and independent data buses: a data-in port for write operation, and a data-out port for read operations. The buses can operate simultaneously. Each data port works at DDR on the same model as the DDR memory: data are transferred on both the rising edge and the falling edge of the clock, thus transferring two data words per clock period. Data are generally transferred by bursts of four data words, which then take two clock periods. The address and control bus is common to read and write, but address and control need to be stable for only one clock period—either for read or for write.

Therefore, during two clock periods, the QDR memory is capable of:

- Receiving a read address and receiving a write address (one clock period each).

- Receiving four data words for write (two data words per clock period).

- Providing four data words for read (two data words per clock period).

These tasks are possible only if the adequate pipelining is employed. Moreover, being an SRAM, QDR memories have no notion of bank, row, column, or refresh like DDR memories. Only the address is necessary to make a read or write operation and the address bus is not multiplexed; rather, it carries the full address. It is possible to have a continuous data flow of two data words per clock period on both the read port and the write port, even if the addresses are random (i.e., not contiguous).

# 2.2.3.2 Manufacturing Aspect

The QDR memories use only CMOS transistors, like any SRAM. There is no specific manufacturing aspect.

# 2.2.3.3 Management of Manufacturing Defects

The QDR memories' target is the industrial market, with the management of manufacturing defects expected to be rigorous.

# 2.2.4 Toggle Magnetoresistive Random Access Memories

Magnetoresistive random access memory (MRAM) is a special type of random access memory (RAM). It has the same characteristics as a RAM (random accesses, fast read and write accesses, no wear in use), but it is also non-volatile (the content is fully preserved when the power supply is cut off). The MRAM combines the advantages of RAM and PROM. The qualifier of "toggle" refers to the method used internally to manage memory cells. Toggle MRAMs are medium-range capacity memories, typically two megabytes per chip.

Very few manufacturers produce toggle MRAM and some of them do so only for their internal usage, without selling them on the market. A significant part of the toggle MRAM market is dedicated to industrial applications, with toggle MRAM rarely found in consumer electronics. For AEH, only one manufacturer produces these memories. This is EVERSPIN, which recently granted licensing rights to one company.

Toggle bit MRAM are used in AEH as non-volatile memory when both of the following conditions exist: a medium storage size is needed (typically a few megabytes) and fast random read and write operations are required. For large amounts of non-volatile data (hundreds of megabytes to gigabytes), toggle bit MRAM is not suitable because of the limited size of the chips. In this case, flash PROM is needed. However, when fast random read and write operations are required, flash PROM is not suitable because of its slow access time, especially for write operation, which additionally requires an erase operation.

Toggle bit MRAM can replace the more classical technologies:

- Electrically-erasable programmable read only memory (EEPROM): the parallel EEPROM market is decreasing. Therefore, EEPROM is not considered a good solution for future designs.

- Non-volatile static random access memory (NVSRAM): NVSRAM is a combination component that contains an SRAM and a PROM on the same die. The user works only with the SRAM, thus enjoying the performance of an SRAM. At power up, the component automatically copies the contents of the PROM into the SRAM. At power down, the component automatically copies the contents of the SRAM into the PROM, thus providing the appearance of an SRAM that keeps its contents across power cycles.

From the functional standpoint, NVSRAM and MRAM are similar. From the standpoint, NVSRAM combines two established technologies (SRAM and PROM), whereas MRAM uses a new technology (magnetic cells).

## 2.2.4.1 Technical Overview

Toggle MRAM uses the physical property of two materials:

• A ferromagnetic material whose magnetic polarization can be changed electrically: once the polarization has been electrically set to a value, the material keeps it until another electrical action changes it. This denotes the toggle element. The change in magnetic

- polarization allows for writing the information into the memory cell. The toggle property of the material provides data retention even after power off.

- A second material whose electrical resistance changes depending on the magnetic field which passes through it. The second element is placed near the first one to be under the influence of its magnetic field. Measuring the electrical resistance of the second element allows for the information of the memory cell to be read.

This system has several advantages:

- Read and write operations are as fast and flexible as with RAM.

- Data retention (unpowered) is as good as with PROM.

- There is no wear out.

The main limitation of the toggle MRAM comes from the method used to electrically change the magnetic polarization of the storage element. An electric current first generates its own magnetic field. This magnetic field, in turn, influences the toggle element and, depending on the electric current direction, changes the toggle element into one state or the other. If two memory cells are too close to each other, the magnetic field generated to toggle the first one may cause the second to toggle, because of proximity, as well. Therefore, the integration factor of toggle MRAM is limited: it is not possible to set the cells too close to one another. Because this limitation comes from physics of the method used to force the toggling, and not from the foundry, toggle MRAM using this method will not see a significant growth in size in the future. Other methods are under development for toggling that do not exhibit this drawback and therefore will allow higher integration (section 2.2.4.4).

Despite the limited integration scale, writing into a cell may still influence a nearby cell, and, in rare cases, cause it to toggle, thus creating a soft error. For this reason, a toggle MRAM chip includes embedded ECC that allows for providing good data at the pins of the chip on read, even when an internal bit is altered.

## 2.2.4.2 Manufacturing Aspect

Although MRAM involves special materials, the fabrication process flow is the same as for standard CMOS RAM. It is even possible to embed toggle MRAM cells in an ASIC. The intrinsic limitation of the toggle MRAM integration may have an unexpected advantage from the point of view of manufacturing defects: as toggle MRAM cannot be scaled down, submicron foundries are not worth using. MRAM uses more conservative technologies, which can reduce the manufacturing efforts and risks. Moreover, the medium-capacity range (16 megabits)—when compared to the DDR memories or flash memories (gigabits)—advocates in favor of risk reduction.

#### 2.2.4.3 Management of Manufacturing Defects

No public information is available about managing manufacturing defects (redundancy, remapping, or other). Components are delivered fully functional and with full capacity.

Embedded ECC seems to aim at mitigating write soft errors (WSEs) but not permanent manufacturing errors.

# 2.2.4.4 Spin Transfer Torque Magneto-Resistive Random Access Memory

Spin transfer torque (STT) MRAM belongs to the MRAM family. The difference between toggle MRAM and STT MRAM resides in the method used to change the magnetic polarization of the ferromagnetic element (section 2.2.4.1). The SST MRAM uses a quantum effect instead of an explicit magnetic field. This reduces the crossover between cells during writing and, therefore, allows for a much greater integration.

SST MRAM technology is seen as possessing high potential for both non-volatile and simple memory, with capacity in the gigabits. The SST MRAM technology is still under development; prototypes exist, but to date there is no mass production. Were STT MRAM to achieve a density level greater than DDR memory, and with equivalent performance, it would likely take the lead in the memory market. Although there is not enough information available to include this technology in the scope of this report, it should be on the watch list for the coming years.

# 2.3 SUPPLY CHAIN CONSIDERATIONS

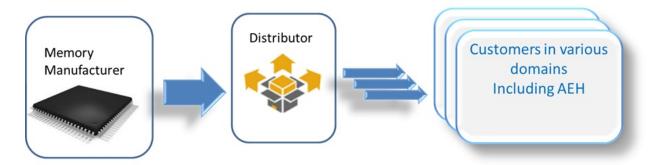

The issues described in the previous section point to the importance of properly selecting the commodity memory manufacturer. This section describes relevant elements in the selection process regarding the supply chain. For the purpose of this report, the supply chain is limited to the manufacturer and distributor (as shown in figure 1), both holding significant roles. Recommendations applicable to the supply chain are proposed in section 5.

Figure 1. Composition of the supply chain for this report

The avionics market represents a very small part of the commodity memories' market. Avionics customers' demands receive a relatively low priority in the eyes of the major memory manufacturers. However, this situation does not prevent avionics equipment manufacturers from obtaining the attention of the memory suppliers nor from acquiring high-quality components. The key is a careful and meticulous selection of the supply chain.

#### 2.3.1 Memory Manufacturers

This section focuses on specific characteristics relevant to the components' supply for avionics applications. Several criteria distinguish the memory manufacturers: targeted market, rate of product upgrade, and available documentation.

#### 2.3.1.1 Targeted Market

The first criterion pertains to the market that is targeted by the manufacturer. Three main cases can be distinguished:

1. Case 1: Manufacturers that have a business model exclusively geared toward consumer electronics

This kind of manufacturer should be avoided or is at least not highly recommended because its mission statement does not entail avionics requirements; as a result, there could be confidence issues associated, for example, with reliability or environmental qualifications. If a given memory component was provided solely by this type of memory manufacturer, this component should be replaced by another one in the design. However, if such a component is necessary, a possible workaround would be to perform complementary tests, such as burning or screening, on the component to increase the level of confidence in the component. These tests can be performed internally or in collaboration with a third party specialized company.

2. Case 2: Manufacturers with a business model that is primarily geared toward consumer electronics but who also have an industrial range of products

This case is more favorable than case 1. The components in the industrial range will be manufactured employing industrial quality standards. The risk of harmful effects from the consumer electronics market is lower. The most favorable case is when the manufacturer has an automotive range of products because the automotive market is a relatively high-volume market with a relatively high-quality set of requirements. This case also includes a safety domain, including rail, nuclear, and medical.

3. Case 3: Manufacturers that have a business model primarily geared toward a specialty market that demands high integrity and continued support

This is the best case because these manufacturers are not, or at least they are significantly less likely to be, subjected to the pressure of the consumer electronics market to compromise quality.

# 2.3.1.2 Rate of Product Upgrade

The second criterion pertains to the upgrade rate of the components. Component modifications, such as die revision (improvement), technology shrink, or component versioning (e.g., memory size or speed), can occur. Sometimes, the manufacturer's strategy is to continuously offer the latest technology with the best available performance. This strategy often leads to negative results, such as short sale duration of products, rapid obsolescence, and a fast process shrinking

rate. The risk induced by this strategy is that the manufacturer might feel it is not worth investing more effort than necessary to increase the production reliability for such a short life cycle.

Another drawback of this strategy, from an AEH point of view, is that the new technology has no service experience and may have intrinsic defects or weaknesses that are not yet known. Moreover, the strategy of being first to market may lead the manufacturers to create temporary revisions of the chips they sell, a fact about which the buyer is seldom properly informed regarding the chips' temporary nature.

As an example, consider manufacturers who sold an intermediate version of their chip by buying equivalent dies from another foundry (a competitor) and repackaged these dies into their own packages with their own references. This approach allows the manufacturer to be present on the market while its foundry ramps up the capability to produce its own dies. From a technical and commercial point of view, there is absolutely nothing wrong with the approach because the dies meet both quality and performance level. However, from the point of view of avionics requirements, for which traceability is a concern, this situation is undesirable. AEH manufacturers should therefore avoid such memory manufacturers. However, this is not always possible because the avionics market has its own goal to keep providing more performance at lower costs. Also, the interest of an avionics manufacturer may primarily stem from obsolescence issues. Well-proven technologies may sometimes be too limited to satisfy the performance requested by a given product. In this situation, particular attention shall be paid to the components, as detailed in section 2.3.1.3. Assiduous contact with the memory manufacturer can help AEH manufacturers to avoid the purchase of new memories that are being manufactured by second-hand manufacturers.

However, other manufacturers rely on well-proven technologies and propose mature components with longer term production cycles. These manufacturers often take over components that were initially provided by the first type of manufacturer. When the first type of manufacturer ceases production (obsolescence), the second type commences manufacturing; as much as possible, this latter type of manufacturer should be preferred.

#### 2.3.1.3 Available Documentation About the Manufacturing Process

A third criterion relates to the availability and extent of documentation. Some memory manufacturers provide documentation on their manufacturing flow, test flow, and qualification processes and results, whereas others do not. The more extensive the documentation, the higher the level of confidence in the product. This kind of documentation is generally not public since it contains intellectual property, but it may be available under a non-disclosure agreement (NDA).

When selecting a manufacturer, the accessibility to manufacturing documentation is an important consideration. There are several major topics addressed by manufacturer documents: design, technology, manufacturing tests procedures, manufacturing tests results (statistics), qualification processes (including a description of the qualification tests), qualification reports (including the detailed test results), errata sheets, and white papers on continuity of support for obsolescence management.

#### 2.3.1.3.1 Information About the Design

Useful examples of this information include:

- Information about the physical proximity of the memory cells on the die with respect to their logical proximity in the address space and data words.

- Information about special internal functions, such as charge pumps, that does not appear in the data sheet.

This information is confidential but may be obtained, at least partially, under an NDA. This information is generally very useful for analyzing risks and mitigation mechanisms. However, special care should be taken because some aspects of the design can change noticeably from one revision of the die to another. For example, memory can be produced in which the relative position of the cells on the die, versus their position in the data words, was significantly different in the successive revisions of the die. It was not a real design change, only a different type of routing—but for ECC consideration, it was an impacting change. Therefore, the relevance level of the design information must always be moderated by its validity in time.

Some design elements may be key points for the memory manufacturer and will, therefore, remain stable across the successive revisions of the memory. For example, the memory manufacturer may have made the commitment to implement a built-in ECC mechanism with a tricky association between the physical cells and the logical bits of the ECC algorithm, so that the ECC is as efficient as possible with respect to the possible soft errors. In this case, if the layout of the cells changes from a die revision to another, the design of the ECC will change accordingly, and the ECC performance will remain unchanged.

To summarize, the information about the design is extremely useful, but it must not be taken as a standalone piece of information. A discussion with the memory manufacturer is absolutely necessary to get the status of each important design choice of a given product and learn whether it is a long-term choice or simply a contextual one.

## 2.3.1.3.2 Information About the Technology

This information is highly confidential and generally not available to the AEH manufacturer. In general, the scheme is as follows:

- The AEH manufacturer can enter into an NDA with the component manufacturer.

- The component manufacturer has an NDA with the foundry.

However, the scheme is not transitive: the component manufacturer cannot transmit the design information, the property of the foundry, to the AEH manufacturer. The foundry will not grant an NDA to the AEH manufacturer because the latter is not one of its direct customers. Even when the component manufacturer runs its own private foundry, the information is often considered as too sensitive and rarely provided.

#### 2.3.1.3.3 Information About Manufacturing Test Procedures

Although this information is essential for addressing most of the concerns within the scope of this report, detailed information is generally not available: first, it is considered highly confidential and, second, it pertains not only to the memory manufacturer but also to the foundry. There may be an advantage, as sometimes general information can be obtained. As a general rule, however, one cannot rely on the availability of this information.

# 2.3.1.3.4 Information About Manufacturing Test Results

Test results are mainly statistics on measured parameters and ratios of accepted, versus rejected, dies. By themselves, they may be very interesting with respect to the objectives of this report. However, once again, this information is rarely available because it is considered highly confidential and pertains not only to the memory manufacturer but also to the foundry. Finally, information about production yield ties to financial information and, therefore, is not disclosed.

# 2.3.1.3.5 Information About the Qualification Process and Associated Report

This information does not concern the whole production set but rather the characteristics of the component itself, measured by way of a limited number of components (generally several hundred). Qualification tests are different from production tests:

- The aim of production tests is to check that the components are manufactured correctly. The result is binary (indicating either okay or not okay).

- The aim of qualification tests is to check that the design and production chain provide chips that have the expected performance. The results have probabilistic values.