# **DOT/FAA/TC-19/22**

Federal Aviation Administration William J. Hughes Technical Center Aviation Research Division Atlantic City International Airport New Jersey 08405

# Use of Virtual Machines in Avionics Systems and Assurance Concerns

October 2019

Final Report

This document is available to the U.S. public through the National Technical Information Services (NTIS), Springfield, Virginia 22161.

This document is also available from the Federal Aviation Administration William J. Hughes Technical Center at actlibrary.tc.faa.gov.

U.S. Department of Transportation **Federal Aviation Administration**

#### NOTICE

This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The U.S. Government assumes no liability for the contents or use thereof. The U.S. Government does not endorse products or manufacturers. Trade or manufacturers' names appear herein solely because they are considered essential to the objective of this report. The findings and conclusions in this report are those of the author(s) and do not necessarily represent the views of the funding agency. This document does not constitute FAA policy. Consult the FAA sponsoring organization listed on the Technical Documentation page as to its use.

This report is available at the Federal Aviation Administration William J. Hughes Technical Center's Full-Text Technical Reports page: actlibrary.tc.faa.gov in Adobe Acrobat portable document format (PDF).

**Technical Report Documentation Page**

| 1. Report No.                               | 2. Government Accession No.        | 3. Recipient's Catalog No.            |

|---------------------------------------------|------------------------------------|---------------------------------------|

| DOT/FAA/TC-19/22                            |                                    |                                       |

| 4. Title and Subtitle                       | 5. Report Date                     |                                       |

| USE OF VIRTUAL MACHINES IN AVI              | October 2019                       |                                       |

| CONCERNS                                    |                                    | 6. Performing Organization Code       |

|                                             |                                    |                                       |

| 7. Author(s)                                | Performing Organization Report No. |                                       |

| Bjorn Andersson, Sagar Chaki, Dionisio d    |                                    |                                       |

| 9. Performing Organization Name and Address |                                    | 10. Work Unit No. (TRAIS)             |

| Software Solutions Division                 |                                    |                                       |

| Software Engineering Institute              | 11. Contract or Grant No.          |                                       |

| Carnegie Mellon University                  | DFACT-14-X-00010                   |                                       |

| Pittsburgh, PA 15213                        | Differ I I II ooo io               |                                       |

| 12. Sponsoring Agency Name and Address      |                                    | 13. Type of Report and Period Covered |

| Federal Aviation Administration             | Final Report                       |                                       |

| 950 L'Enfant Plaza                          |                                    |                                       |

| Washington, DC 20024                        |                                    | 14. Sponsoring Agency Code            |

|                                             |                                    | AIR-6B4                               |

15. Supplementary Notes

The FAA William J. Hughes Technical Center Aviation Research Division Technical Monitor was Srini Mandalapu.

16. Abstract

Virtual Machine (VM) technology uses a hypervisor that creates multiple virtual copies of a computer, each to be used by a single application as if it was the only one running. This virtual copy, known as a VM, must be isolated from the other VMs. The industry is considering VMs and hypervisors for efficiency and flexibility of computing resources. For the certification of avionics systems, this isolation is a valuable asset that potentially allows modularity of certification and recertification. As a result, this study evaluated current VM technology and similar technologies as they relate to the assurance of avionics systems.

The research was focused on assurance issues, verification in particular, in which virtualization technologies are implemented in avionics systems. Verification of new technologies is challenging to certification authorities. To investigate this aspect of VM, the research studied verification technologies for VMs. This study was divided into timing verification and logical verification. From the timing perspective, multiple verification techniques were proposed that are generic enough to model virtualization; the tradeoffs among them were documented. From the logical verification side, different techniques that require different degrees of human involvement, from fully automated (e.g., model checking) to more interactive (e.g., theorem provers), were documented. The research also highlighted the assurance data that can be affected by the porting of an application from single to multicore processors and the use of hardware emulation to try to preserve the behavior of the original hardware.

Virtualization in software architecture is an increasingly common practice in the software industry, and it is not surprising there is interest for airborne systems. This research provided several recommendations and conclusions on the use of VMs in airborne systems. The research results will be used in developing guidance and training material for the certification engineers. The research also recommends additional research on isolation and verification techniques for improved modular recertification and fostering corresponding standards, solutions for the impact of multicore on virtualization technology, and verification schemes for virtualization implementations.

| virtualization implementations.                                                                                                |                                      |                                            |                                                                                                 |                                            |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|

| 17. Key Words                                                                                                                  | 18. Distribution Statement           |                                            |                                                                                                 |                                            |  |  |

| Avionics systems, Virtual machines, Virtualization, Safety assurance, Hypervisor, Verification technologies, Worst-case timing |                                      | National Technical<br>Virginia 22161. This | available to the U.S.<br>Information Service<br>document is also avail<br>tion William J. Hughe | (NTIS), Springfield, able from the Federal |  |  |

| 19. Security Classif. (of this report)                                                                                         | 20. Security Classif. (of this page) |                                            | 21. No. of Pages                                                                                | 22. Price                                  |  |  |

| Unclassified                                                                                                                   | Unclassified                         |                                            | 206                                                                                             |                                            |  |  |

# ACKNOWLEDGEMENTS

| The SEI team thank | as the FAA team, | in particular Sr | rini Mandalapu, fo | or feedback on this report. |

|--------------------|------------------|------------------|--------------------|-----------------------------|

|                    |                  |                  |                    |                             |

# TABLE OF CONTENTS

|      |                                                                                                                                                                                                                                                                                                                                         | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| EXEC | CUTIVE SUMMARY                                                                                                                                                                                                                                                                                                                          | vii  |

| 1.   | SURVEY OF LITERATURE RELATED TO VIRTUAL MACHINES                                                                                                                                                                                                                                                                                        | 1    |

| 2.   | ASSURANCE ISSUES ON VIRTUAL MACHINES IN AVIONICS SYSTEMS                                                                                                                                                                                                                                                                                | 1    |

| 3.   | EVALUATION OF VERIFICATION TECHNOLOGIES FOR VIRTUAL MACHINES                                                                                                                                                                                                                                                                            | 2    |

| 4.   | COMPOSITIONAL VERIFICATION FOR VIRTUAL MACHINES                                                                                                                                                                                                                                                                                         | 3    |

| 5.   | SINGLE-TO-MULTICORE PORTABILITY OF ASSURANCE DATA                                                                                                                                                                                                                                                                                       | 3    |

| APPE | NDICES                                                                                                                                                                                                                                                                                                                                  |      |

|      | A—SURVEY OF LITERATURE RELATED TO VIRTUAL MACHINES B—ASSURANCE ISSUES ON VIRTUAL MACHINES IN AVIONICS SYSTEMS C—EVALUATION OF VERIFICATION TECHNOLOGIES FOR VIRTUAL MACHINES D—COMPOSITIONAL VERIFICATION FOR VIRTUAL MACHINES E—SINGLE-TO-MULTICORE PORTABILITY OF ASSURANCE DATA F—IDENTIFICATION OF ASSURANCE ISSUES ON EMULATION OF |      |

|      | CERTIFIED HARDWARE G—FUTURE WORK AND RECOMMENDATIONS                                                                                                                                                                                                                                                                                    |      |

#### LIST OF ACRONYMS

API Application programming interface

BVT Borrowed-Virtual-Time

CARTS Compositional Analysis of Real-Time Systems

CFG Control flow graph

CMAS Certifiable Multicore Avionics Systems

COTS Commercial off-the-shelf CPU Central Processing Unit

CRPD Cache-related preemption delay

CS Critical section

DAG Directed acyclic graph

DM Deadline monotonic

DMA Direct memory access

DMS Deadline monotonic scheduling

DRAM Dynamic random-access memory

DTM Dynamic thermal management

EDF Earliest-Deadline First

EVM Embedded virtual machine

EVT Extreme value theory

EX Execution

FIFO First-in, first-out FPS Frame per second

FR-FCFS First-ready, first-come, first-served

ID Instruction Decoding

IF Instruction Fetch

IMA Integrated modular avionics

I/O Input/output

IOMMU Input/output memory management unit

IPC Instructions per cycle LCM Least common multiple

MC/DC Modified condition/decision coverage

MEM Memory Access

MILS Multiple Independent Levels of Security/Safety

MMU Memory management unit

MPCP Multiprocessor Priority Ceiling Protocol

MPSoC Multiprocessor systems on chips

NOP No operation OS Operating system

PALS Physically Asynchronous Logically Synchronous

PCP Priority Ceiling Protocol

PI Priority Inheritance

PSO Partial Store Order

QoS Quality of service

rbf Request bound function

RM Rate monotonic

RMS Rate-monotonic scheduling

RTES Real-time embedded systems

RTOS Real-time operating systems

RTV Real-time virtualization

SAT Satisfiability

sbf Supply-bound function SC Sequential consistency

sEDF Simple Earliest-Deadline First

SEU Single event upset

SLA Service-level agreement

SMT Satisfiability modulo theories

SRAM Scratchpad RAM TD Time division

TDM Time-division multiplexing

TDM+FP Time-division multiplexing plus fixed-priority scheduling

TLB Translation lookaside buffer

TSO Total Store Order

TTA Time-triggered architecture UDR Utility degradation resilience

V&V Verification validation VC Verification condition VM Virtual machine

MCD Wittual Machine

vMCP Vector Mixed-Criticality Packing

VMM Virtual machine monitor

WB Result Write Back

WCET Worst-case execution time

WCRT Worst-case response time

ZSRM Zero-slack rate-monotonic

#### **EXECUTIVE SUMMARY**

Virtual machine (VM) technology uses a hypervisor that creates multiple virtual copies of a computer, each to be used by a single application as if it were the only one running. This virtual copy, known as a VM, must be isolated from other VMs. For the certification of avionics systems, this isolation is an invaluable asset that can potentially allow modularity of certification and recertification. This report evaluates current VM technology and similar technologies as they relate to the assurance of avionics systems.

This report is divided into seven sections. The first section provides a literature survey that tracks the origin of virtualization and explores related isolation techniques and verification technologies. This survey tracks the different motivations and goals of the virtualization technologies. In particular, the survey identifies how the initial virtualization objectives were focused on simplicity of development and use with a strong emphasis on throughput. Clearly, throughput has been a key driver of general-purpose computing but hinders the worst-case (timing) behavior needed to provide assurance of real-time systems. The section presents an alternative isolation mechanism focused on real-time behavior.

The second section on assurance issues discusses specific issues of assurance when virtualization technologies are used in avionics systems. In particular, the section discusses how the goals of assurance of avionics systems relate to different virtualization technologies and how different innovations in the hardware layers interact with virtualization. It also discusses how recent innovations in real-time systems deal with hardware innovations to ensure predictable timing behavior.

The third section focuses on verification technologies for VMs. This section is divided into timing and logical verification. For timing, the study presents multiple verification techniques that are generic enough to use to model virtualization and discuss the tradeoffs among them. For logical verification, it presents different techniques that require different levels of user involvement, from fully automated techniques, such as model checking, to more interactive techniques, such as theorem provers.

The fourth section discusses compositional techniques for verification. This section enhances the discussion of the previous section with a more focused discussion on compositionality and modularity aspects. In particular, it discusses the brittleness of the modules, the interfaces that these techniques offer, and their effect on modular certification.

The next two sections discuss the portability of assurance data from single to multicore, and the emulation of hardware. These sections are closely related. The first section highlights the assurance data that can be affected by porting an application from single to multicore processors; the second section covers the use of emulation hardware to try to preserve the behavior of the original hardware.

In the final section, conclusions and recommendations are presented. The section starts by presenting gaps in two main research areas: 1) missed opportunities in the modularity aspects to improve recertification, and 2) the challenges that multicore processors present to virtualization given that hardware shared across cores creates delays that break current isolation techniques. For

spatial virtualization, one of the key missed opportunities is the lack of verified hypervisor implementations that can support a verifiable isolation. As a result, our main recommendations are: 1) additional research on more modular isolation and verification techniques, and developing the corresponding standards; 2) additional research on solutions for the impact of multicore in virtualization technology; and 3) research on additional implementation-verification schemes to support verified isolation for full virtualization.

#### 1. SURVEY OF LITERATURE RELATED TO VIRTUAL MACHINES

This report surveys related work on virtual machines (VMs) with the most common implementations present today. It complements the assurance issues document that discusses at length the implications of using VMs for the assurance of avionics systems (see appendix B).

This document starts by introducing the history of VMs dating back to the 1960s and defines the initial principles and goals. This is followed by reviewing the resurgence of VMs in the late 1990s, which continues today. The document then moves into a discussion of the products and systems that are available today with their main characteristics. The product discussion briefly highlights only the differences and points out the related concepts previously introduced. A more elaborate discussion will be presented in the assurance issues document.

Section 4 covers technology related to virtualization. This section discusses other technologies that also have the same or similar goals as virtualization: namely, to create some form of partition by which applications can execute in an isolated manner. In particular, two forms of virtualization are discussed: 1) temporal virtualization in section 4.1, and 2) spatial virtualization in section 4.2. Under temporal virtualization, a brief introduction on background in rate-monotonic scheduling is given to discuss processing servers that have recently been integrated in VMs aimed at providing real-time guarantees. Similarly, variations of resource reservation that are being investigated for mixed-criticality scheduling are presented, followed by a brief discussion of more traditional forms of temporal partitioning (virtualization) based on time slots.

Under spatial virtualization, section 4.2 discusses different variations of spatial protection that are traditionally implemented as variants of kernels. The discussion includes the traditional monolithic kernel, the microkernel, and two kernels that are more specialized: the security kernel and the separation kernel. All of this is put into the perspective of today's VMs in section 4.2.5. This is followed by a brief discussion of technologies for development partitioning that, although not providing full virtualization, help the developer to isolate its work and the configuration of its system. This is discussed in section 4.3.

To understand the impact on certification that VMs may have, there is a section on analytic technologies that covers temporal analysis and logical analysis. The overview of temporal analysis focuses on the technology related to analysis of systems that use VMs. Each of the works in this section involve modifications to the mechanisms to make the timing behavior predictable and analyzable. The overview of logical analysis starts with testing, then moves to exhaustive verification with techniques like model checking and theorem proving, and discusses the related tools. Finally, section 5 highlights some implications related to safety standards, in particular to DO-178B/C.

## 2. ASSURANCE ISSUES ON VIRTUAL MACHINES IN AVIONICS SYSTEMS

Virtualization is an old concept originating in the early days of mainframe computing to hide the physical details of the hardware platform from applications. It has regained popularity recently with the advent of cloud computing, which essentially turned mainframe computing from a concept of physically centralized computing to virtualized computing. The original benefits

remain. New benefits include relief from the maintenance and operational responsibilities associated with owning and managing a data center.

Advances in virtualization technology have led to the development of efficient hypervisors and minimal VMs. This has led to considering VMs as vehicles for deploying services that require different operating environments on a single platform managed by a hypervisor. This approach can enable security, interoperability, evolvability, and modifiability in many types of systems. However, their use in safety- and timing-critical environments, such as avionics systems, has not been fully studied.

Virtualization provides both a computing platform that mimics specific hardware and operating system (OS) platforms and isolates applications operating within a VM from affecting the VM or any other application under the control of the VM. The question for safety- and timing-critical systems is whether the isolation is strong enough that applications executing within a VM have suitably predictable behavior. Specifically, VMs need to allow for making strong guarantees about applications' timing and spatial access correctness.

With this in mind, this report discusses the key concepts of the structure and function of VMs and virtualization technology, identifies the characteristics of VMs and virtualization that support and are inimical to achieving timing and access correctness, and exposes the benefits and challenges that VMs and virtualization pose for certifying systems.

This report is organized as follows: Section 1 introduces VMs. Section 2 discusses the goals of VMs and the properties they exhibit in terms of isolation and partitioning with respect to different hardware resources. It goes particularly deep into how different innovations at different levels of hardware work together to improve throughput but may hinder worst-case response time (key for real-time systems). It then discusses the adaptations and analysis innovations that the real-time community has developed to make the hardware innovations predictable and allow it to build temporal isolation on top. Section 3 discusses the additional certification complexity that the use of VMs can incur, from both the logical and the timing correctness points of view. Section 4 compares the isolation characteristics provided by VMs with other technologies to explain VMs' advantages and limitations. The development process issues are discussed in section 5, highlighting how the partitioned development environment can help distribute development evenly across organizations. Section 6 then puts all the previous discussion within the context of certification standards. Section 7 presents conclusions.

#### 3. EVALUATION OF VERIFICATION TECHNOLOGIES FOR VIRTUAL MACHINES

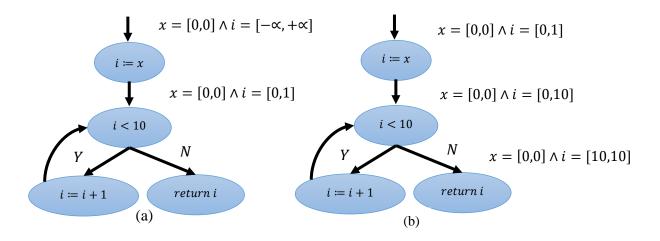

In this report, we evaluate verification technologies for VMs. These technologies cover both timing and logical verification. This report complements the "Assurance Issues on VMs in Avionics Systems" report (appendix B). As such, it does not include technologies already included in that report, such as rate-monotonic scheduling, but instead focuses on technology not previously discussed. Because only a few of the current verification technologies have been tailored to VMs, we take a wider approach, discuss general techniques, and highlight adaptations or potential uses for VMs where appropriate.

This report is divided into sections: "Timing Verification" and "Logical Verification." The timing verification section covers real-time calculus, timed automata-based analysis, and worst-case execution time (WCET) analysis. The WCET analysis subsection is further subdivided into measurement-based analysis and model-based analysis to present methods suited for different confidence levels, like the ones related to DO-178B/C Software Levels.

The logical verification section starts with techniques that require more user involvement, such as testing and theorem proving, and moves into techniques that are fully automated, like model checking. A subsection of abstract interpretation is included in both the timing and logical verification sections, but the former is tailored to bound WCET, whereas the latter is tailored to verifying logical properties.

For each of the techniques covered in this report, we discuss their benefits, limitations, and applicability using examples where deemed helpful.

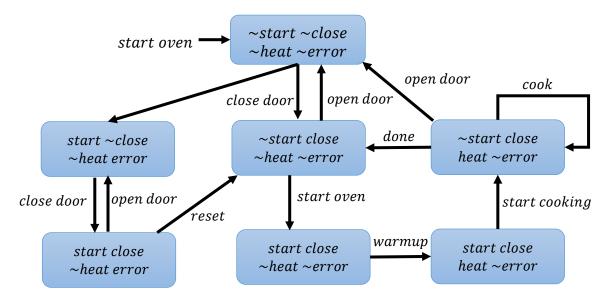

## 4. COMPOSITIONAL VERIFICATION FOR VIRTUAL MACHINES

Virtualization offers the possibility of isolating components and potentially verifying them independently from one another. Certification standards, like DO-178C, require such an isolation to allow the verification of an individual component without the need to recertify all components. However, the isolation among components offered by virtualization is not absolute, either because they need to interact with each other or because they share hardware resources. This means that users of these techniques for verification must be aware of the interactions across components. The research community calls this type of verification compositional verification.

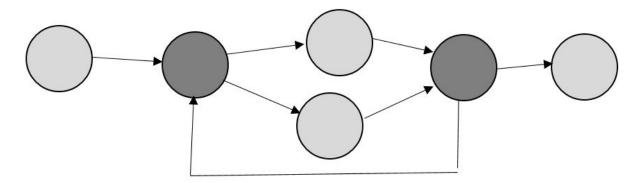

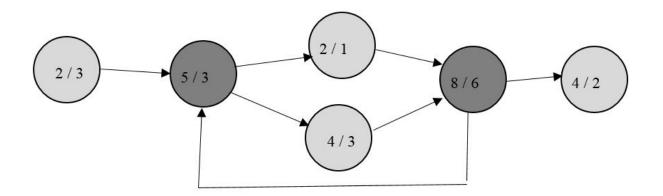

Compositional verification defines components whose behavior can both be affected by other components and affect other components only through an interface. With this definition, the verification process is decomposed into two parts. First, components are verified by taking into account their interactions with other components observable through the interface. Second, the whole system is verified as a collection of components connected through their interfaces, whose behavior is limited to what is observable through the interface. These interfaces are influenced by both the verification technology and the mechanisms that restrict the behavior, such as a VM and its hypervisor.

In this report, we study the compositional technologies that support the use of different types of virtualization to enable independent component verification both from the timing and logical perspectives. Section 2 discusses virtualization interfaces from both the perspective of timing and functional correctness. Because timing is changed as a result of virtualization, we emphasize timing in our discussion. Section 3 presents mitigation strategies. Section 4 gives recommendations.

## 5. SINGLE-TO-MULTICORE PORTABILITY OF ASSURANCE DATA

The use of multicore processors in avionics has received increasing interest. There are two reasons for this: 1) commercial availability and 2) performance. With respect to commercial availability, single-core chips are simply not available from many chip vendors; if buying processor chips from such a vendor, then a multicore chip is the only option. With respect to performance, multicore

processors offer advantages over single-core processors. These advantages include: 1) the potential for parallel execution of threads in multicore processors, and 2) lower power consumption and lower thermal dissipation, therefore reducing the need for advanced cooling and power generation. The potential for parallel execution is particularly helpful for software systems that are already multithreaded; this is typically the case for avionics. Reducing the needs for advanced cooling and power generation are important for application domains in which size, weight, and power requirements are important; this is also typically the case for avionics.

This increasing interest in using multicore processors in avionics raises a question: How do we certify aircraft that use multicore processors? This report discusses this question—particularly, what can go wrong when porting software originally developed for a single-core processor now must execute on a multicore processor?

#### APPENDIX A—SURVEY OF LITERATURE RELATED TO VIRTUAL MACHINES

## A.1 INTRODUCTION

Virtualization is a broad term for software used to create, from one resource, software entities so that each software entity behaves like the resource. Different types of resources can be virtualized, such as processors, memory spaces, network interface cards, communications links, or entire networks. In this report, we focus mostly on virtualization of one or more processors. Virtualization offers the following benefits:

- Lower hardware cost: Virtualization allows for creating multiple machines from one physical machine.

- Support for multiple machines with slight differences: If many virtual machines (VMs) have many instructions in common, then they can execute natively, and only a small number (but different for each VM) of instructions needs to be simulated.

- Support for legacy hardware: In some cases, software has been developed in the past for old hardware that is no longer commercially available. It may be, however, that new hardware supports most of the instructions from the old hardware, and therefore a virtual machine monitor (VMM)<sup>1</sup> can be used running on the new hardware to create a VM of the old hardware.

- Security<sup>2</sup>: If malware infects one operating system (OS), other OSs for other VMs are unaffected (assuming that the VMM is not affected). For example, if you want to download some code from the web or visit a website that you are suspicious of, then you can do so in a VM. If the VM gets infected, it does not affect other VMs. You just kill your VM, and the malware will have no lasting effect on your machine (assuming that it does not write to a durable medium).

- Privacy: Because VMs have non-overlapping address spaces, it holds (under certain assumptions<sup>3</sup>) that execution within one VM cannot infer behavior of another VM.

In the next section, we will discuss the history of VMs.

#### A.2 HISTORY

The history of VMs can be traced back to the 1960s. In this section, we focus on three seminal papers that capture the historic roots of this technology.

-

<sup>&</sup>lt;sup>1</sup> Also called a hypervisor.

There is a known defect in some dynamic random-access memories (DRAM), known as row hammer. The defect allows a program to access one memory location and thereby modify other memory accesses. In this way, one VM could modify memory used by another VM or the VMM. See [A-1].

So-called timing attacks are possible. Specifically, VMs execute instructions that read from and write to memory; when they do so (for most processors), they attempt to read from or write to a so-called cache memory (a small, fast memory that stores frequently accessed data items). A memory access from VM A may bring its data into the cache so that it can access this memory address again. In the meantime, it may happen that VM B accesses a memory address in a way that evicts the data that VM A brought. Therefore, VM A can detect the existence of another VM; it can even infer that a memory access to a certain subset of memory addresses has been made.

#### A.2.1 POPEK AND GOLDBERG

One of the most authoritative works on virtualization is the article by Popek and Goldberg [A-2]. This work aims to state conditions for virtualization, but it also provides a tutorial and a survey. It states, "a virtual machine is taken to be an efficient, isolated duplicate of the real machine." Because the VM must be efficient, it follows that using one processor to simulate two or more processors will lead to a large slowdown, and therefore it is not virtualization. The authors point out that most of the instructions must be executed natively on the physical processor; for virtualization to take place, software is allowed to simulate only a few instructions. They state explicitly that:

The second characteristic of a virtual machine monitor is efficiency. It demands that a statistically dominant subset of the virtual processor's instructions be executed directly by the real processor, with no software intervention by the VMM. This statement rules out traditional emulators and complete software interpreters (simulators) from the virtual machine umbrella.

The authors describe virtualization with the following concepts: 1) a VMM is a piece of software that provides an environment for programs that is essentially identical with the original machine, 2) programs executing on this VM show at worst only minor decreases in speed, and 3) the VMM is in complete control of system resources.

Popek and Goldberg [A-2] point out that a VM will be slower because: 1) the VMM requires time, and 2) other VMs consume system resources. Popek and Goldberg [A-2] provide us with the following definition of a VM:

**Definition:** A virtual machine is the environment created by the virtual machine monitor.

Later they provide another definition of a VM:

**Definition:** Then functionally, the environment which any program sees when running under the control of a virtual machine monitor present is called a virtual machine.

From this definition, the article by Popek and Goldberg [A-2] points out that:

... a VMM as defined is not necessarily a time-sharing system, although it may be.

Note that isolation is not mentioned as one of the three properties of a virtual machine. It is because it is implied; we state that it provides an environment for execution; it executes on the virtual machine as if it were on a real machine and this implies isolation.

The focus of the work by Popek and Goldberg [A-2] was on so-called third-generation machines. This term is not used today, but it may be instructive to know what it means. First-generation machines used vacuum tubes; the second generation used transistors. Third-generation machines are characterized by the use of integrated circuits, and they have linear addressable memory. Examples are the IBM 360, Honeywell 6000, or DEC PDP-10. The fourth generation uses microprocessors, and the fifth generation provides artificial intelligence. Today, we have fourth-generation computers, but the work by Popek and Goldberg [A-2] on third-generation computers is still relevant to our discussion.

Popek and Goldberg [A-2] assumed that processors have two modes of operation: 1) supervisor mode and 2) user mode. The former has access to all instructions of the machine, but the latter does not necessarily have that. The authors also assumed that the computer has a memoryrelocation register and that the instruction set consists of the usual operations: arithmetic, testing, branching, and moving data in memory. Computers today use multilevel paging and sometimes segmentation rather than relocation registers, but today's paging mechanism can function in a similar way as relocation registers. The authors assume that the VMM consists of three modules: 1) a dispatcher, 2) an allocator, and 3) an interpreter. The dispatcher "catches" traps. The allocator decides which memory addresses to allocate a VM. The interpreter executes so-called sensitive instructions (these are instructions that the hardware cannot execute directly). The authors specify how a sensitive instruction can be performed. The idea is that a machine can be modeled as having a state, and the instruction can be modeled as transitioning from one state to another. The authors state that we can describe a sensitive instruction with a set of pairs of states (from state, to state). The implementation of a sensitive instruction can be done with a table lookup. This method is not supposed to be used (because it is not efficient with respect to memory), but it is presented to show that sensitive instructions can be simulated.

The article by Popek and Goldberg [A-2] points out that a VM differs from a real machine in only two ways: timing and resource control. Therefore, later parts of this document will describe methods for virtualization while satisfying timing requirements.

The main result of Popek and Goldberg's work [A-2] is a sufficient condition for virtualization on third-generation computers. The condition is that if each sensitive instruction is a privileged instruction, then virtualization is possible. This is a sufficient condition, but it is not necessary.

Popek and Goldberg [A-2] end the paper by defining a "hybrid virtual machine." This is a VM in which all virtual-supervisor mode instructions are interpreted. This results in lower efficiency (lower execution speed), but it has the advantage of allowing virtualization on architectures in which the Popek and Goldberg sufficient condition is false.

## A.2.2 BUZEN AND GAGLIARDI

Buzen and Gagliardi [A-3] provide a tutorial and survey the evolution of VMs in the 1960s and 1970s. They argue that one should build the system software as one small part that is assumed correct and another part that is everything else. They stress that a VM behaves as a real machine, but its timing may be different because 1) the VMM has overhead and 2) other VMs may be running concurrently. They also point out that the VMM does not perform instruction-by-instruction interpretation of programs. They emphasize that reliability is an important aspect of VMs; an operating system can be tested in one VM, and if it crashes then it does not crash other VMs. They stress isolation as one goodness property. They mention that in virtualization, VMM intervention of input/output (I/O) devices can make it possible to create I/O devices that have no physical analog, such as a tape that behaves like a disk. Buzen and Gagliardi [A-3] defined a VM as:

A basic machine interface which is not supported directly on a bare machine but is instead supported in a manner similar to an extended machine interface is known as a virtual machine.

This definition is similar to the definition by Popek and Goldberg [A-2], but it emphasizes the interface rather than the environment.

Buzen and Gagliardi [A-3] discuss early VMs from the perspectives of 1) processor state mapping, 2) memory mapping, and 3) I/O mapping. With respect to 1), they mention that the VMM has a virtual status indicator so that when the VM executes an instruction that reads the status indicator, it traps and the VMM reads the virtual status indicator in the VMM and returns the value. Writes to the virtual status indicator are handled analogously. With respect to 2), they mention that the VMM maps pages for processes running under VMs. They point out that for interrupt service routines, it is often the case that the address where instructions of interrupt service routines start must be stored at a fixed location in memory, and a VM should not be allowed to change that. Therefore, the VMM must set up the virtual-to-physical address translation of the VM. With respect to 3), they mention a situation in which a program executing on a VM initiates the execution of a channel program. This is implemented by the VMM copying this program to certain fixed addresses and then executing this program; after getting the result, it copies it back to the VM. It is noteworthy that Buzen and Gagliardi [A-3] point out that paging systems are not necessary for virtualization; they state that any memory relocation mechanism that can be made invisible for nonprivileged execution is enough. They stress (as did Popek and Goldberg [A-2]) that trapping of sensitive instructions is an absolute requirement for virtualization.

Buzen and Gagliardi [A-3] mention that later generations of VMs ran on computers that supported paging. This made it possible to have recursive virtualization; that is, one VM can provide multiple VMs. Buzen and Gagliardi [A-3] point out that, in later systems that support paging, it may be necessary to perform address translation twice: from application processes' virtual address to the perceived physical address of the operating system to the actual physical address. To perform this double mapping efficiently, the VMM computes a composed table. Buzen and Gagliardi [A-3] discuss Type-2 virtualization, in which a VM is created on top of a normal operating system. When a new VM is created, the VMM informs the underlying operating system that traps should be directed to the VMM.

#### A.2.3 GOLDBERG

Goldberg [A-4] presents two taxonomies about virtualization: Type-1 virtualization and Type-2 virtualization. In the former, the VMM runs directly on the hardware. In the latter, the VMM runs on top of a privileged software nucleus. For the latter, when the VMM starts a new VM, M, the VMM needs to notify the privileged software nucleus that when a trap is generated from within M, it should not be dealt with by the privileged software nucleus; instead, it should be directed to the VMM.

The term emulation is often used if the virtual machine is very different from the machine executing the VMM.

Goldberg [A-4] does not define a simulator, but this term is typically used to mean the same thing as an emulator except that the system is not simulated with as high fidelity. The separation kernel is a related concept, but it focuses more on security and confidentiality (see sections 4.2.3 and 4.2.4).

#### A.3 PRODUCTS AND SYSTEMS

The concept of VMs dates back to the 1960s, but had a revival in the late 1990s and early 2000s because of the increasing use of data centers and data warehouses, particularly for server processing of Internet applications. In this era, software developers wanted to offer applications accessible through a web browser and run the applications on a web server. This could be achieved if the software developer ran his or her web server. However, many software developers preferred to outsource server administration to focus on developing more and better software functionalities. Therefore, a new breed of companies for hosted service emerged. These companies found VMs useful because they could run multiple VMs, each for different clients, on a single physical machine. This approach saved hardware costs and cooling costs and allowed migrating one VM to another VM in case of overload (or hardware failure) of one physical machine.

From this era, two products are noteworthy: VMWare<sup>TM</sup> [A-5] and Xen<sup>TM</sup> [A-6]. They differ in how they deal with sensitive instructions. VMWare uses binary translation, and Xen uses paravirtualization. These products are discussed in section A.3.1.

## A.3.1 VMWARE

VMWare is a private corporation in Palo Alto, CA, that sells VMMs and related products. It was founded in 1998 and later acquired. It claims to be the first company to virtualize x86 processors, which are hard to virtualize.

The cofounders of VMware wrote an article describing their first product VMware workstation [A-5]. This product was based on two ideas: 1) the VMM identifies basic blocks in a VM and detects whether, in a basic block, there is a sensitive instruction (if so, it calls a subroutine in the VMM); and 2) the product used software emulation of I/O devices. The former implies that it can run unmodified operating systems. The latter implies that all VMs experience the same hardware; this brings the benefit that if a VM named V is hosted by a real computer R1, then one can stop V and restart it on another computer, R2, even if R1 and R2 have different I/O devices. This facilitates load balancing.

Today, VMWare offers a wide range of products: both Type-1 and Type-2 VMMs and products for both desktops and servers. Among the products from VMWare, ESX/ESX is perhaps the best known.

#### A.3.2 XEN

Xen was developed in Cambridge, UK, in the early 2000s. It was developed as an open-source VMM of Type 1 (i.e., the VMM executes directly on the processor), and it changed certain operating systems (Windows® XP, Linux® kernel, and NetBSD) to operate together with this VMM. The changes to these operating systems were made to improve performance; the authors of [A-6] mention that their VMM can support 100 VMs. This idea of modifying an operating system running in a VM so that it performs well when running under a VMM is called para-virtualization; it is an old idea that had a revival in the early 2000s. Xen was originally developed for the x86 processor architecture, and its creators [A-6] list the difficulties in virtualizing x86. Some of the difficulties include the following: 1) Like most processors, some instructions are intended to be used only in privileged mode; 2) normally, such an instruction is executed in non-privileged mode,

then it generates a trap, but in x86 they fail silently; and 3) because these sensitive instructions fail silently, the VMM cannot intercept them. The paper [A-6] mentions that VMWare ESX can handle this, but at the expense of lower performance, and VMWare ESX modifies the code in the guest operating system if there are instructions that exhibit this silent failure<sup>4</sup>.

The authors of the paper [A-6] refer to their VMM as a hypervisor because it executes at a higher privilege than the normal operating system in a VMM (which can be thought of as supervisor mode). Xen took the following design decisions:

- Each guest operating system is responsible for memory management.

- The VMM is copied in the address space of each VMM, which avoids flushing of the translation lookaside buffer (TLB).

- Whenever the guest OS needs a new memory page, it allocates one from its own reservation and notifies the VMM.

- On x86, there are four privilege levels. Applications run in privilege level 1, and the operating system runs in privilege level 4. However, with Xen, the operating system runs in privilege level 3, and Xen runs in privilege level 4; this ensures that Xen runs with a higher privilege level than respective guest operating systems.

- When a processor invokes a system call (by generating a trap; i.e., software interrupt), then it yields control directly to its corresponding guest operating system (i.e., not to Xen). This is done because system calls are common, and it is important that they are performant.

- When a process generates a page fault, then it transfers control to Xen, to privilege level 4; the reason for this is that a page fault handler needs to know the address that generated the page fault, and this information is only accessible in privilege level 4.

- When a new VM is started, admission is performed, and this admission control is not executed in Xen; it is executed in a guest operating system (the reason for this is to keep the hypervisor small and to separate policy from mechanisms: mechanisms should be implemented in the Xen hypervisor, and policies should be implemented elsewhere).

- A guest operating system can invoke services from Xen using a hypercall (similar to a system call), and Xen can notify a guest operating system using events (similar to UNIX signals).

Xen refers to VMs as domains. There is one special domain called Domain0; it handles policy matters, I/O, and scheduling parameters. In the original version of Xen, central processing unit (CPU) scheduling of domains was done with the algorithm Borrowed-Virtual-Time (BVT) [A-7]. This algorithm works as follows:

-

<sup>&</sup>lt;sup>4</sup> Intel has introduced a new mode in its x86 processors to avoid this.

- 1. Each processor has an actual virtual time and an effectual virtual time.

- 2. The process with the lowest effectual virtual time is selected.

- 3. At each time quantum, the actual virtual time of a process is incremented by an amount that is equal to the elapsed time multiplied by the share proportion of the process.

- 4. The effectual virtual time of a process is set to actual virtual time of the process, but the process can temporarily get a boost by getting this effectual virtual time decreased further.

The BVT is claimed to be designed for low-latency applications, but there is no known schedulability analysis for it (i.e., there is no method for proving that processes meet real-time deadlines when this scheduler is used). Later versions of Xen added two new schedulers: simple Earliest-Deadline First (sEDF) [A-8] and credit scheduler [A-9]. The sEDF scheduler characterizes a process with three parameters (period, execution time, and a flag stating whether it can reclaim time) and schedules processes with Earliest-Deadline First (EDF). The credit scheduler operates with virtual timers that are updated in a similar manner as BVT.

As mentioned, Xen was originally developed for x86, but today it supports many other architectures (ARM, PowerPC, MIPS). Recently, it has been claimed<sup>5</sup> that it offers superior performance compared to other open-source hypervisors.

With the popularity of virtualization, a large number of VMM products came out. Some are listed in sections A.3.4–A.3.7.

## A.3.3 HYPER-VTM

Hyper-V [A-10, A-11] is a hypervisor developed by Microsoft<sup>®</sup>. It is a Type-1 hypervisor, and it is released as a component of Windows Server<sup>®</sup>. It supports VMs with Windows or VMs with the Linux kernel. Hyper-V runs on X86-64 processors and uses the VT-X x86 virtualization feature.

#### A.3.4 KVM<sup>TM</sup>

KVM [A-12] is open-source software that turns the Linux kernel into a hypervisor. It is a Type-1 hypervisor. KVM can create VMs for a wide range of processors—x86, S/390, PowerPC, and IA-64—and a wide range of guest operating systems—Linux, BSD, Solaris, Windows, and OS X. It supports para-virtualization for Ethernet cards and disk controllers.

## A.3.5 VIRTUALBOX<sup>TM</sup>

VirtualBox [A-13] is a Type-2 hypervisor that is partially available as open source. A core package is open source, but support for certain I/O devices is proprietary software. VirtualBox can run on top of many of the common desktop operating systems, and it can create VMs with many of the common operating systems.

See "Ubuntu 15.10: KVM vs. Xen vs. VirtualBox Virtualization Performance," http://www.phoronix.com/scan.php?page=article&item=ubuntu-1510-virt

Hypervisors have also been developed for real-time, safety-critical, and secure systems. Two are listed in sections A.3.6 and A.3.7.

#### A.3.6 RT-XEN

RT-Xen [A-14] is a project to add real-time scheduling algorithms to Xen. RT-Xen supports global Earliest-Deadline First and global fixed-priority preemptive scheduling. These are schedulers used within RT-Xen, not schedulers within guest operating systems. RT-Xen also supports four server-based mechanisms (a polling server, periodic server, sporadic server, and deferred server); these are discussed in more detail in section 4.1.1.1. These mechanisms allow the attachment of a server period and server budget to a VM so that the VM will consume only a certain amount of processing power within a certain time window (how these time windows are generated depends on the specific server mechanism used). Today, parts of RT-Xen have been incorporated in the normal Xen hypervisor.

# A.3.7 XMHF

XMHF [A-15] is a research prototype developed at Carnegie Mellon University. It is a hypervisor that supports a single VM. Its merit is that formal verification has been performed to prove memory integrity; that is, the hypervisor's memory can be modified only by instructions that are an intended part of the hypervisor.

## A.4 RELATED TECHNOLOGY

VMs have not been the only technology development that has pursued the goals of system partitioning, isolation, and protection. In this section, we discuss related technologies that share similar goals as VMs.

## A.4.1 TEMPORAL VIRTUALIZATION

Temporal virtualization in VMs is traditionally achieved with a two-level scheduler assigning a time slice in a round-robin fashion to each VM and letting the scheduler inside the VM schedule its processes internally [A-6]. This approach is aimed at fairness, but it may cause problems in real-time settings because it ignores deadlines. Some versions of real-time double scheduling exist today [A-14, A-16].

In real-time systems, where meeting thread (or task) deadlines are important, temporal virtualization takes the form of temporal protection. More specifically, real-time tasks interact with physical processes in a continuous fashion (they execute forever) through some form of periodic interactions or reactions to physical events. The execution of each interaction/reaction is known as a job. The interval between job activations (also called arrivals) is known as period or minimum inter-arrival time. These jobs are required to finish their execution within a fixed time from its activation, known as a deadline. Real-time systems use real-time schedulers that determine when tasks execute and analysis to verify whether all tasks will always finish by their deadlines; that is, whether the task set is schedulable. Temporal protection in this context implies that a task's misbehavior, such as executing longer than its specified worst-case execution time (WCET) or activating more frequently than its specified period, will not make other tasks miss their deadlines.

#### A.4.1.1 Reservations

Resource reservation is a scheme to provide temporal guarantees and isolation of tasks that use time-shared resources. This applies not only to CPU time but also to other resources, such as network, memory bandwidth, cache, and disk bandwidth.

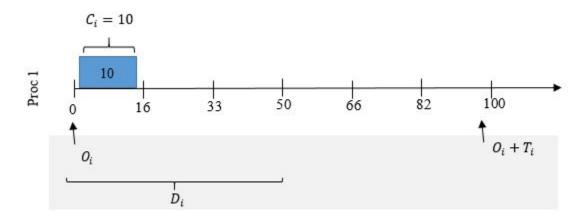

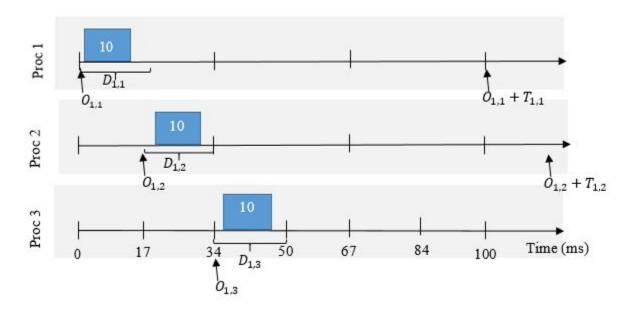

Resource kernels [A-17, A-18] combine generalized rate-monotonic scheduling (RMS) theory [A-19] (that includes deadline monotonic scheduling, or DMS), and processing servers provide resource reservation and achieve temporal protection. Specifically, RMS relies on three elements. First, a scheduling mechanism known as fixed-priority scheduling ensures that the highest-priority task that is ready to execute is given the processor; if a higher-priority task becomes ready, it preempts<sup>6</sup> the currently running task. Second, an offline priority assignment gives higher priority to tasks with smaller periods (or deadlines, if they are not at the end of the period). Third, analysis algorithms verify that tasks meet their deadlines. These three elements—classified here as mechanism, configuration, and analysis—guarantee that tasks meet their deadlines if their specified parameters (WCET and period) are not violated (e.g., because of misbehavior).

For RMS, the mechanism is fixed-priority scheduling, the configuration is the assignment of higher priorities to tasks with shorter periods, and one of the analysis methods is the response-time test. The response-time test [A-20] uses the recurrence equation:

$$R_i^k = C_i + \sum_{j < i} \left[ \frac{R_i^{k-1}}{T_j} \right] C_j,$$

(A-1)

where the N tasks  $(\tau_i)$  of the system are indexed with indices 1 to N in increasing order of period (or deadline, if different) that matches the increasing order of priority in RMS and defined with the following parameters: period  $(T_i)$ , WCET  $(C_i)$ , and deadline  $(D_i)$ . The equation may need to be evaluated multiple times as it is defined in terms of the previous value of itself (i.e.,  $R_i^k$  is defined in terms of  $R_i^{k-1}$ ). For instance, for two tasks  $\tau_1 = (T_1 = 4, D_1 = 4, C_1 = 2), \tau_2 = (T_2 = 8, D_2 = 8, C_2 = 3)$ , we can calculate  $R_1 = C_1 = 2$ , given there are no tasks with higher priority (smaller index) than  $\tau_1$ .  $R_2$  can be calculated as  $R_2^0 = C_2 = 3, R_2^1 = (C_2 = 3) + \left[\frac{R_2^0 = 3}{T_1 = 4}\right](C_1 = 2) = 5, R_2^2 = (C_2 = 3) + \left[\frac{R_2^1 = 5}{T_1 = 4}\right](C_1 = 2) = 7, R_2^3 = (C_2 = 3) + \left[\frac{R_2^2 = 7}{T_1 = 4}\right](C_1 = 2) = 7$ . In this case, multiple repetitions were necessary to make the equation converge in step 3  $(R_2^2 = R_2^3)$ . Given that in both cases the response time is smaller than the deadlines  $((R_1 = 2) \le (D_1 = 4))$  and  $(R_2 = 7) \le (D_3 = 8)$ , the tasks are schedulable.

It is worth noting that RMS analysis does not require that the tasks activate at the same time or in any particular sequence of time offset between them (such as in phasing). This means that tasks can be added or removed while other tasks are running if the offline analysis deems the modified task set schedulable with the new priority configuration (priority assignment) without making the old tasks miss their deadlines. This assumes that there is enough idle CPU cycles to reassign priorities.

-

When a task x is preempted by a task y, the execution of x is paused until task y finishes. Then the execution of task x is resumed.

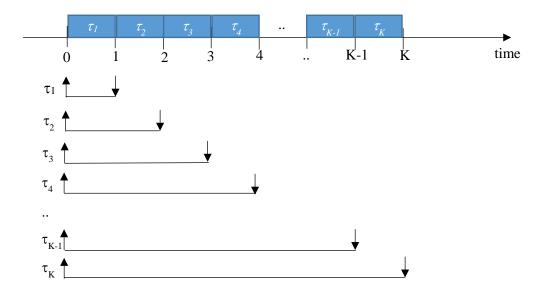

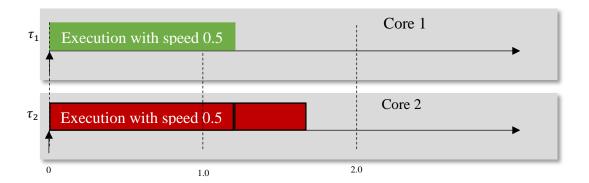

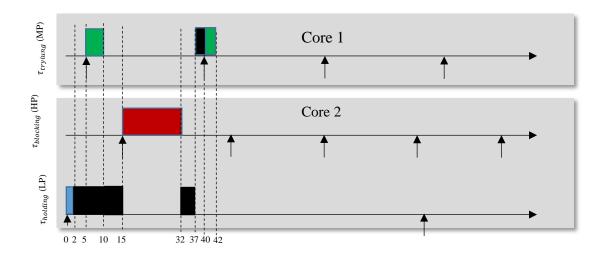

To understand why RMS is not sensitive to activation phases between tasks, it is useful to compare figures A-1 and A-2.

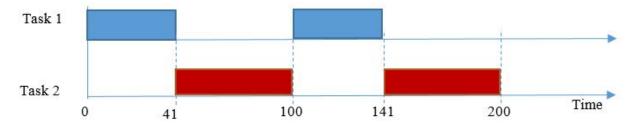

Task 1: Period = 100, WCET = 41, Priority = 2; Task 2: Period = 141, WCET = 59, Priority = 1

Figure A-1. Worst-case phasing of two tasks (both tasks start at zero)

Figure A-1 shows a Gantt chart of two tasks. The colored boxes represent the time tasks take to execute on the processor. In this case, both tasks are ready to execute at time 0, and the fixedpriority scheduler chooses Task 1, which has a higher priority (assigned according to RMS). We can see that after Task 1 completes at time 41, Task 2 starts and finishes its WCET (59) at time 100, just in time for the second arrival of Task 1 (after its period of 100 elapses). Task 1 finishes at time 141 just in time for the second arrival of Task 2 (after its period of 141 elapses). It is worth noting that the pattern exhibits execution of the tasks one after another without leaving any idle time in the processor. This means that it is not possible for any of the tasks to execute for longer periods or to add any other task. This was proven [A-21] to be the worst-case situation for any set of two tasks for any period and any WCET. Moreover, it is possible to observe that the ratio of the period of Task 2 to Task 1 is roughly equal to the square root of 2:  $\frac{141}{100} \cong 2^{\frac{1}{2}}$ . The sum of the utilizations (utilization =  $\frac{WCET}{Period}$ ) is roughly equal to the square root of 2 minus 1 multiplied by 2:  $\frac{59}{141} + \frac{41}{100} \cong \frac{82}{100} \cong 2\left(\frac{141}{100} - 1\right)$  (in the proof they are equal). This calculation gives a bound that can be used to perform a fast test on any task set of two tasks:  $2(2^{\frac{1}{2}}-1)$ . For instance, we can test whether the two tasks in figure A-1 are schedulable by evaluating  $\frac{41}{100} + \frac{59}{141} \le 2\left(2^{\frac{1}{2}} - 1\right)$ . This bound was generalized to task sets of any size *N*:  $N(2^{\frac{1}{N}} - 1)$ .

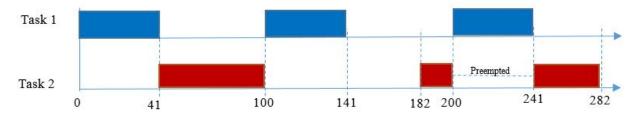

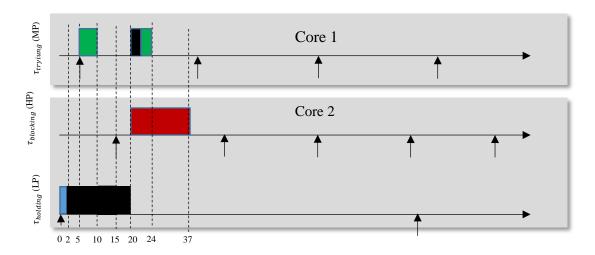

To complete the discussion on phasing, figure A-2 shows the same two tasks but with Task 1 starting at time 0 and Task 2 at time 41. In this case, the idle time from 141 to 182 (and a preemption of Task 2 by Task 1 from 200 to 241) is shown. This means that, if we consider the worst-case phasing, processing time may be wasted, but there is a gain in simplicity of evaluation and flexibility to start the tasks at any time. That is, to take advantage of this idle time, it is necessary to force the phasing shown in figure A-2.

Task 1: Period = 100, WCET = 41, Priority = 2; Task 2: Period = 141, WCET = 59, Priority = 1

Figure A-2. Another phasing (Task 1 starts at 0 and Task 2 at 41)

## A.4.1.1.1 Servers

Software defects can lead to timing misbehavior in a task by causing it to execute beyond its WCET or more often than anticipated. Mechanisms known as servers [A-22–A-25] were developed to prevent this misbehavior from affecting the timing guarantees of other tasks. Whereas these mechanisms are known as servers in the real-time literature, the term processing servers will be used in this report to avoid conflicts with other type of servers (e.g., web, database) and just servers when the context is clear. When processing servers are used, tasks are assigned to servers, and the scheduler runs the tasks assigned to the server based on the server parameters. Each server has a budget and a replenishment interval or period. With these parameters, the server behaves as a periodic task with its deadline at the end of its period (with the budget as the WCET and the replenishment interval as the period), allowing the use of RMS analysis to verify the schedulability of a set of servers. This is the behavior of the periodic server [A-25]. In this case, as a task assigned to a server executes, it decrements the budget. If the budget reaches zero, the task is paused. The budget is replenished after the replenishment interval has elapsed, and the paused task (if any) resumes executing.

Servers have priorities and the same priority scheduling applies as in tasks in RMS. Tasks assigned to a server execute with the server's priority. When only one task is assigned to each periodic server, the server replenishment interval can be synchronized with the task's periodic activation, and the server budget is equal to the WCET of the task. The server guarantees the following properties: 1) it allows the task to execute for its WCET, but 2) prevents it from executing beyond; 3) it allows two activations of the task to be as close as one replenishment interval apart but 4) prevents shorter intervals. Properties 1 and 3, combined with a successful scheduling analysis of the servers, guarantee the schedulability of the tasks. Properties 2 and 4 ensure that any misbehavior of the task is prevented from affecting the schedulability of other tasks. Given that servers are not required to have synchronized activations, servers can be added or removed without inducing deadline misses just as with the scheduling of tasks.

When servers are used with multiple tasks, more complex schedulability analysis is required whether or not the tasks' WCET and periods are synchronized with the servers' budgets and periods. To understand this, how the server budget is consumed should first be discussed. Specifically, for the periodic server to behave as a periodic task, it needs to start consuming its budget as soon as it is activated if it has the highest priority among the active servers. This is an assumption of the RMS analysis. This means that if the task is running (highest-priority ready server), the budget must be decremented as time passes, even if no task is executing. This creates

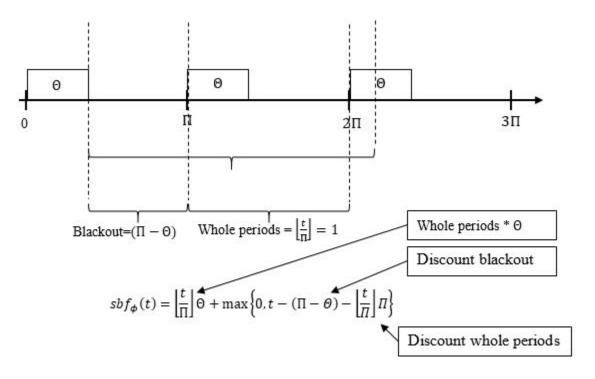

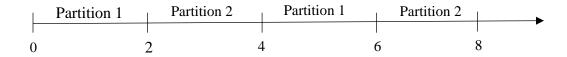

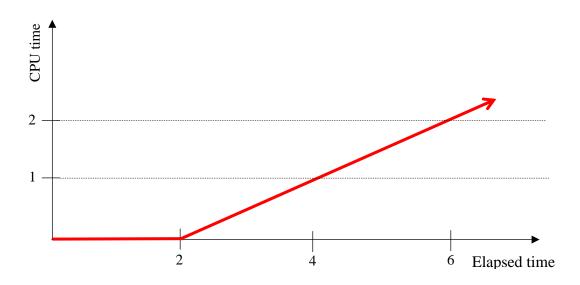

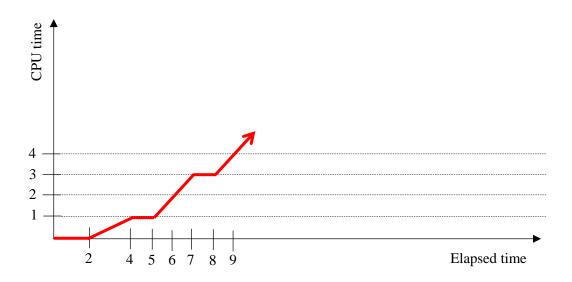

"blackout" intervals for tasks if a task arrives just after the server's budget was exhausted (taking into account the worst-case response time calculation), and the blackout will last until after the next replenishment and all higher-priority servers execute. These unsynchronized effects also apply when multiple tasks are run on a single server. New scheduling algorithms have been created to take this into account [A-26]. Motivated by the drawbacks of the unsynchronized periodic server, three other variants of servers were created: the deferrable server, the sporadic server, and the polling server. The deferrable server [A-22] decrements the budget only when a task is executing. Whereas this prevents blackouts, the server does not behave as a periodic task anymore because it creates a back-to-back preemption for lower-criticality servers. That is, a task running on a high-priority server can execute at the end of the replenishment interval, exhausting the budget at exactly the same time the next replenishment is due. Then, because the budget is replenished at that time, the same task can continue executing. This means that lower-priority tasks will experience a preemption equivalent to two back-to-back WCET within an interval equal to the period, breaking the original assumption of periodic tasks (i.e., there is only one WCET within a period). A modified schedulability analysis has been created to take this into account [A-22].

To correct back-to-back execution, the sporadic server was created [A-24]. In this case, the budget is again consumed only when a task executes, but the replenishment is modified. Specifically, the portion of the budget consumed by the execution of a task is replenished only after an interval equal to the server period has elapsed from the start of executing such a task. This way, if the task consumes the budget at the end of the replenishment interval (as in the back-to-back case of the deferrable server), the replenishment does not happen immediately when the budget is exhausted (as in the deferrable server) but instead one full server period after the task started executing. This mechanism recovers the behavior of the periodic task but makes the replenishment mechanism more complex. To reduce this complexity, the polling server was created [A-27]. The polling server periodically checks whether a task is ready to execute and, if so, it executes the task with its budget. In this case, it also creates a blackout, but it is tailored to simplify the mechanisms.

Resource kernels [A-17, A-18] generalized processing servers into what is called resource reservations. A resource reservation is a reservation to use a resource. When the resource is CPU cycles, it maps directly to processing servers, and the reservation is described in terms of CPU time budgets with some periodicity, deadline, and other parameters. Resource reservations are implemented in resource kernels as an operating system object with a handler in the same fashion as a file and its file handler. A reservation handler is "attached" to a process ID for that process to run within the "processing server" implemented by the reservation. This means that the execution of the process is restricted to consume only the CPU assigned to the reservation and, therefore, the same scheduling analysis that we have discussed for processing servers can be applied.

Multiple processes can be attached to a reservation, and all the processes attached to a reservation will share the budget allocated to this reservation. At the same time, the temporal protection offered by the reservation prevents processes running in one reservation from interfering with the processes running in another reservation. It is worth noting that when a reservation is created, the resource kernel runs an internal schedulability test to verify that it is possible to execute the reservation within the requested parameters (budget, period). This test is called an admission test, ensuring that any new reservation is guaranteed by the timing analysis theory. Reservations can be created at runtime if the timing analysis theory does not require the reservations to be synchronized. This simplifies updates because parts of the system that need to be added or removed

on the fly can be without disturbing the other parts of the system. This can be ensured by letting the admission test run in the idle time left by the running reservations (i.e., running this code at a lower priority than the reservations).

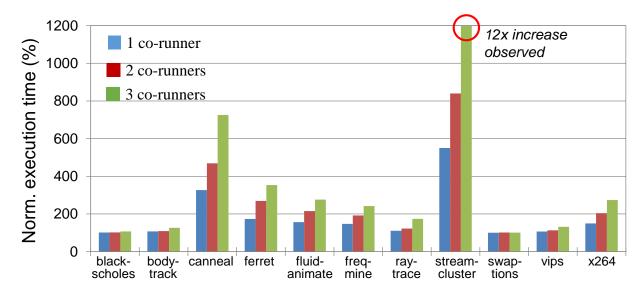

Resource reservations go beyond CPU cycles. In particular, they allow the reservation of other resources, such as network [A-28], disk [A-29], cache [A-30], and even RAM memory [A-31]. Both cache and RAM memory are critical resources that must be properly managed in multicore processors. This is because a task running in one core can delay the execution of another task running in a different core due to access to the common cache, RAM memory, or both. This approach has shown increases of up to six times when compared to a task running alone in legacy applications and more than 14 times for synthetic cases [A-31].

The protection of resource kernels is based on ensuring that task deadlines are always respected without over-constraining the execution to specific time slots. Multiple issues must be addressed when tasks interact with each other, such as when they use mutexes or semaphores to synchronize. The reserve inheritance is one of these solutions [A-32]. When multiple resources are used together, such as when the disk scheduler needs CPU time to process a disk request, it is necessary to verify the combined requirements [A-29].

# A.4.1.2 Mixed-Criticality Isolation

Temporal isolation typically implies protecting a task from delays imposed by other tasks to prevent a deadline miss. This isolation is identified as a symmetric protection, given that protecting Task A from Task B also implies protecting Task B from Task A. However, certification documents assign different criticalities to different tasks. This implies that it is necessary to verify that the probability of failure of a high-criticality task should be smaller than those of lower criticality, and the corresponding verification should be imposed. In real-time scheduling, all the scheduling algorithms are proven mathematically, assuming that a task cannot execute more than its stated WCET. Because the WCET is very difficult to calculate, it is a common engineering practice to obtain it through conservative experimental measurements. If variations from the external environment can be isolated, it is possible to use abstract interpretation [A-33] to obtain a better bound. In the end, a probability of not exceeding the WCET can be calculated, and different methods (and their probabilities) can be applied to tasks with different criticalities.

This has given rise to a new scheduling approach in which tasks with different criticalities are assigned different execution times. The schedulability of tasks is then verified at their assigned level of criticality, assuming that their WCET and the tasks that can delay them are bound by the WCET at this criticality level [A-34]. This way, an asymmetric temporal protection is achieved (i.e., a high-criticality task is protected, assuming that only tasks with criticality levels the same or higher can interfere with it). This applies to each criticality level; when the schedulability of a lower-criticality level (e.g., Level 1) is verified, it is assumed that higher-criticality tasks (Level > 1) execute for the WCET calculated at Criticality Level 1.

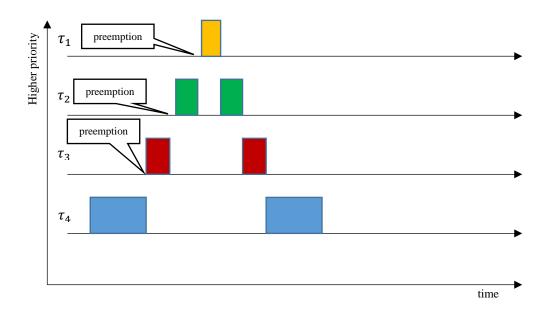

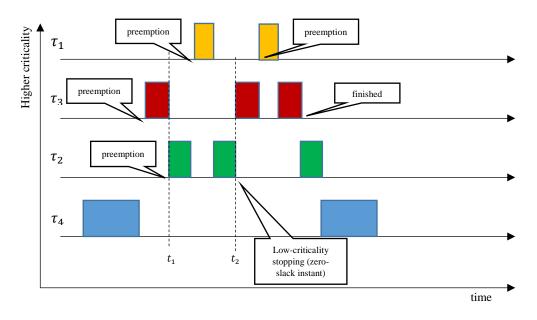

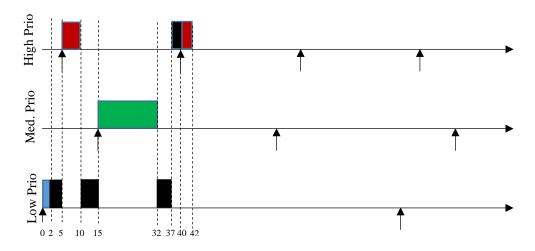

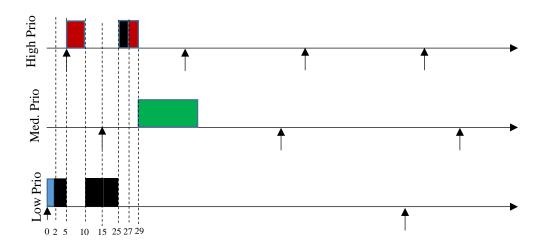

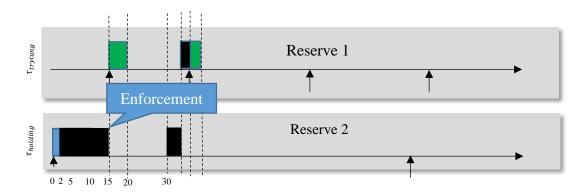

A number of scheduling approaches have been developed [A-35, A-36]. Zero-slack rate-monotonic (ZSRM) scheduling is one of these approaches [A-37]. ZSRM scheduling is based on RMS but adds a mechanism that suspends low-criticality tasks at what is called a zero-slack instant calculated offline. This zero-slack instant  $Z_i$  divides the execution of a task  $\tau_i$  into parts or modes:

the normal mode and the critical mode. During the normal mode, all tasks run; in the critical mode, only tasks that have higher or equal criticality than  $\tau_i$  execute. ZSRM scheduling uses the response time equation A-1 to calculate the zero-slack instant and to verify the schedulability of the tasks. However, tasks that interfere with task  $\tau_i$  in equation A-1 also must include all lower-priority but higher-criticality tasks  $\tau_j$ , given that  $\tau_j$  may enter its critical mode and suspend  $\tau_i$ . In this case, we need to take into account only the portion of  $\tau_j$  that runs in critical mode. In ZSRM scheduling, tasks can be classified in any number of criticalities but only have two WCET parameters, known as nominal execution time  $(C_i)$  and overloaded execution time  $(C_i)$ , in addition to period  $(P_i)$ , deadline  $(D_i)$ , and criticality  $(\zeta_i)$ .

To illustrate how ZSRM scheduling works, consider the following two tasks:  $\tau_1 = (P_1 = D_1 = 4, C_1 = C_1^o = 2, \zeta_1 = 1)$  and  $\tau_2 = (P_2 = D_2 = 8, C_2 = 2.5, C_2^o = 5, \zeta_2 = 2)$  with zero-slack instants  $Z_1 = 4, Z_2 = 5$ . The response-time test of  $\tau_2$  can then be divided in nominal mode  $R_2^n$  (before  $Z_2 = 5$ ) and the critical mode  $R_2^c$  (after  $Z_2$ ) with the execution time split into nominal execution time ( $C_2^n = 2$ ) and critical execution time ( $C_2^c = 3$ ) adding to its overloaded execution time ( $C_2^o = 5$ ). This is calculated as:  $R_2^{n(0)} = (C_2^n = 2), R_2^{n(1)} = (C_2^n = 2) + \left[\frac{R_2^{n(0)} = 2}{T_1 = 4}\right](C_1^o = 2) = 4$ , and  $R_2^{c(0)} = (C_2^c = 3)$ ,  $R_2^{n(1)} = (C_2^c = 3) + \min\left(Z_2 = 5, \left[\frac{R_2^{c(0)} = 3}{T_1 = 4}\right](C_1^o = 2)\right) = 8$ ,  $R_2^{n(2)} = (C_2^c = 3) + \min\left(Z_2 = 5, \left[\frac{R_2^{c(0)} = 3}{T_1 = 4}\right](C_1^o = 2)\right) = 8$ . In this case, equation A-1 was modified to include the *min* function that captures the fact that after  $Z_2$ ,  $\tau_1$  is suspended and does not add to the response time of task  $\tau_1$ . By

captures the fact that after  $Z_2$ ,  $\tau_1$  is suspended and does not add to the response time of task  $\tau_1$ . By design  $Z_2$  is calculated to make  $\tau_2$  finish at its deadline. Now, because there are no tasks with lower criticality than  $\tau_1$ , its zero-slack instant is set to its deadline:  $Z_1 = D_1 = 4$ . This means that it never executes in critical mode. However, when calculating its response time, it needs to be taken into account that the fraction of  $\tau_2$  runs in critical mode because, during that execution,  $\tau_1$  is suspended. In addition, only the WCET from  $\tau_2$  at the criticality level of  $\tau_1$  is considered. In ZSRM, this is the nominal execution time ( $C_2 = 2.5$ ), which applies to any criticality level lower than  $\zeta_2$ . Furthermore, the execution time that  $\tau_2$  was able to complete in its nominal mode before  $Z_2$  ( $C_2^n = 2$ ) can be discounted; that is, only ( $C_2 = 2.5$ ) – ( $C_2^n = 2$ ) = 0.5 units of execution are considered. As a result,  $R_1^n$  can be calculated as  $R_1^{n(0)} = (C_1^0 = 2)$ ,  $R_1^{n(1)} = (C_1^0 = 2) + \left[\frac{R_1^{c(0)} = 2}{T_2 = 8}\right] (C_2 - C_2^n = 0.5) = 2.5$ ,  $R_1^{n(2)} = (C_1^0 = 2) + \left[\frac{R_1^{c(1)} = 2.5}{T_2 = 8}\right] (C_2 - C_2^n = 0.5) = 2.5$ .

It is worth noting that, because only the nominal execution time of tasks with higher criticality than  $\tau_i$  are considered to calculate its response time, ZSRM scheduling guarantees  $\tau_i$ 's schedulability only if no task  $\tau_j$  with higher criticality than  $\tau_i$  exceeds its nominal execution time  $C_i$ .

ZSRM scheduling has been extended for multiprocessors [A-38], multimodal systems [A-39], utility-based systems [A-40], and tasks that synchronize with mutexes [A-41].

<sup>&</sup>lt;sup>7</sup> See [A-16] for the calculation of the zero-slack instant.

## A.4.1.3 Time-Triggered Architecture

Time-triggered architecture (TTA) [A-42, A-43] is a design methodology and supporting mechanism that allows the building of a distributed real-time system based on a globally synchronized clock completely activated (triggered) by a time-triggered bus. This synchronization allows some time-fault detection and recovery mechanisms based on the absence of messages expected to occur at specific times and the presence of unexpected messages at specific times. TTA is implemented with a bus guardian mechanism that follows a strict schedule of message receptions and transmissions that are specified at design time. The time of the bus is the global time to which all nodes are synchronized. The guardian prevents message transmissions or receptions that are not part of the schedule (of each application). This feature is what implements the temporal virtualization and protection. Given that perfect synchronization is not possible, a time granularity is selected according to the capability of the hardware implementation. For instance, in the implementation discussed in [A-42], this granularity is 60 ns.

To build a system with TTA, it is necessary for each node to specify its schedule of communication (transmission and reception) that satisfies the requirements from the applications, such as periodicity, deadlines, and execution times. The node schedules are then integrated into the global bus schedule to ensure that all the nodes' timing constraints are honored. The final schedule is typically computed with constraint-solving approaches like mixed-integer linear programming or satisfiability modulo theories (SMTs) [A-44]. Such methods often take a long time. Furthermore, modifications to the applications frequently require a global recomputation of the task schedule and the bus schedule, making this method very sensitive to changes.

TTA has a number of derived technologies, mostly related to networks. Among them we can find the time-triggered Ethernet [A-45], the time-triggered controller area network [A-46], and—to an extent—FlexRay [A-47].

# A.4.1.4 Integrated Modular Avionics